Maitham S. Khuraibut. International Journal of Engineering Research and Applications www.ijera.com ISSN: 2248-9622, Vol. 12, Issue 4, (Series-I) April 2022, pp. 53-59

## RESEARCH ARTICLE

**OPEN ACCESS**

# **Multivibrators-Astable and Monostable IC**

Maitham S. Khuraibut

## ABSTRACT

The study was prepared with the aim of implementing a High Quality Monostable and A stable Multivibrators by Using 555 Timer, A commercially available IC. The study established that 555 Timer IC is a critical device, most pronounced economical and applicable in the global technology industry and reliable actual timing device which can apply either as a basic timer to produce single pulses or overhaul delays, or rather relaxation oscillator generating and emitting a trend of stabilized wave-forms of diversified duty patterns trending from 50 to 100%. The method used thereto comprise of practical observation as a methodology. Where from the study the capacitors should have charges of non-other than 1/3 VCC to 2/3 VCC as equivalent to the period the output value is high. Research recommend industries with circuit work oriented tasks to go for this technology as it is economical and well manageable.

Date of Submission: 04-04-2022

# I. INTRODUCTION

The 555 Timer is primarily applied in place of IC modified to allow a multiple of output wave transmissions in conjunction with an external RC connectivity. It is probable and practically evident that Multivibrators interlinked with CMOS Oscillators can effectively be produced from a detached element to bring about relaxation oscillators which generate basic square wave transmission patterns by Izawa. Although, there are also pre-modified IC's particularly modified to precisely transmit the reliable output wave-trend alongside other few superfluous timing elements.

This device has been on use right from the era of IC's and on its own it is known among the most critical components in the industry of technology, "standard" as a phrase in this field is pin-pointed to a 555 Timer Oscillator which is basically referred to as the "555 Timer" (Vojtasek). The primary value model 555 Timer draws its name from ground which there are three internal affixed  $5k\Omega$  resistors which it employs when generating the twin comparators reference voltages.

According to Everest, the 555 Timer IC is a critical device, most pronounced economical and applicable in the global technology industry and reliable actual timing device which can apply either as a basic timer to produce single pulses or overhaul delays, or rather relaxation oscillator generating and emitting a trend of stabilized wave-forms of diversified duty patterns trending from 50 to 100%.

A Multivibrators circuit is primarily a nonsinusoidal circulating device with an alternating output. It is a twin developed circuit interlinked into a 0,1 or 2 compiled output stationary devices. With regards to the frequencies of intact elements there are three groups of Multivibrators circuits explicitly; Bistable Multivibrator installed with twin stable states, Monostable Multivibrators installed with a single stable state and Astable Multivibrators installed with a zero stable states (GONG et al.).

Date of Acceptance: 19-04-2022

On instances where Monostable and Bistable Multivibrators and exterior trigger wave is needed for particular actions, Astable Multivibrators is asserted to automate the interior wave output interconnected with switches for progressive emission on the double lined states both for a SET AND RESET. Normally, there are double key elements in each Multivibrators such as; the Bistable circuit and the two passive interconnectivities which are located in a basic feedback loop(Vojtasek). The interchanging connectivity within the circuit can either be Monostable (resistive), Astable (resistive capacitor) or Bistable. Astable Multivibrators is installed alongside double amplifying phases which are interlinked to a significant feedback loop through double restrictive-capacitor with basic networks. The components applied in place of amplifying the wave-forms may be a meeting point area effect transistors, bipolar end points, operational amplifiers or any other kind of amp.

The 555 timer IC was established for the first time in 1970 by the SDignetics Corporation as the SE555/NE555 which referred to as "Timer IC Time Machine" as detailed by Izawa. This was the only identified commercial timer system around. It facilitated circuit manufacturers with a somewhat economical, potential, one unique all-purpose

interconnected circuit asserted in the Multivibrators equipment.

The IC is inclusive of a total of 23 transistors, 2 diodes alongside the 16 resistors compounded within the element which can sustain high temperature in case of a drift. The voltage monitor contains some three resistors with equal value of  $5K\omega$  beneath the bipolar version of the IC, which made the device to be termed as 555.

### Objective

The Specific objective of the study is to implement a High Quality Monostable and A stable

Multivibrators by Using 555 Timer, A commercially available IC

# Content

# -Methods

The primary external instrument of the Astable Timer is identified under the capacitor. The requirements as speculated are such as; the resistors and capacitors of measurable values. The capacitors should have charges of non-other than 1/3 VCC to 2/3 VCC as equivalent to the period the output value is high(GONG et al).

The voltage in the capacitor at any charging point is provided as;

Vc=VCC (1-et/RC)

Given period for capacitor to pick charge to a preferred level of +1/3 VCC t1=1/3 VCC = VCC (1-et/RC)).

Therefore, by choosing the best values to assert C and R in the frequencies of 0.001uf to 100uf and  $1K\omega$  to  $10K\omega$ , from this method, we can denote the expected results in terms of frequencies directly off the homograph which paves a way to outdo the

probable errors which might come to existence (Izawa).

### II. RESULTS

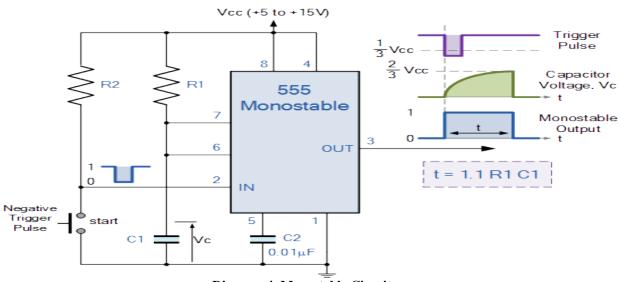

The process begins right from when the first single pulse degenerates. The criteria referred to as a "one-shot", this is reinforced when a negative progressive pulse is entailed on to the trigger comparator. The trigger comparator responds to the progressive pulse generated but not above (1/3 VCC), the node triggers the pulse which raises the output High.

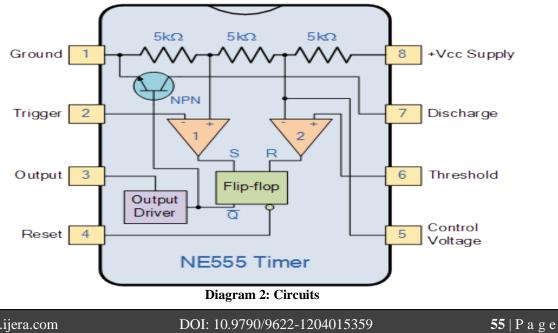

After pulse are triggered, the discharge output is switched OFF where the capacitor C interconnected from outside begins charging to the top most degree through the resistor R. The maximum output pulse reaches its end upon the full charging of the capacitor to a level of 2/3 VCC by Nagaraj. The internal process in line with the IC 555 in monostable system mode over the RC timing circuit is presented in diagram 2 and 3.

The found results can be summarized as follows. The discharge transistor undergo saturation. The capacitor C, linked to the open collector draws its significance from discharge path. At the end of everything, the capacitor discharges fully and voltage becomes 0. The output at pin 3 is also found to be zero (0).

From the values asserted above, Amonostable 555 Timer is probable to offer a time lapse in the circuit flow. From the given values, where 10uf timing capacitor was employed, the value of resistor being looked upon to derive 500ms time delay as the average output. This is equivalent to 0.5s as shown in the calculation below:

$R_{-} = \frac{t}{1.1C} = \frac{0.5}{1.1 \times 10 uF} = \frac{0.5}{1.1 \times 10 \times 10^{-6}} = 45.5 k\Omega$

The above calculations depict that the degree for timing resistor which can bring about time constant of 500ms is found to be  $45.5 \text{K}\omega$ . Although, this value does not represent a standard value resistor, hence need to go for nearest value of  $47 \text{K}\omega$  that is present in every standard ranges of tolerance picking from the E 12 (10%) to the E 96 (1%). Providing therefore a new valued time delay of 517ms.

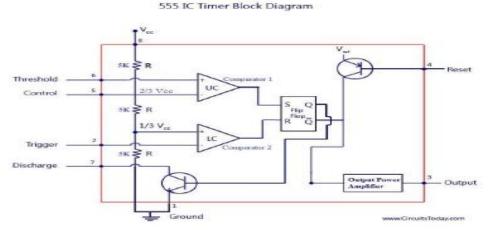

From the results and analysis above, the study pin-points the components packed thereto, in the 555 timer. Below is a flow diagram presenting the functionality of 555 to the latter. The figure

shows the comparators, also referred to as the Two op-amps), there is the R-S flip-flop, double transistors as well as a resistive interconnection.

The Resistive devices comprise of three equivalent resistors (5K Ohms each R) and provides as a voltage divider. Literally, the resistor connectivity is modified in a manner which can ration the voltage beneath the inverting terminal installed in Comparator or rather Upper Comparator 1 to 2/3 Vcc and stage the non-inverting junctions of Comparator 2 also termed as Lower Comparator to 1/3 Vcc

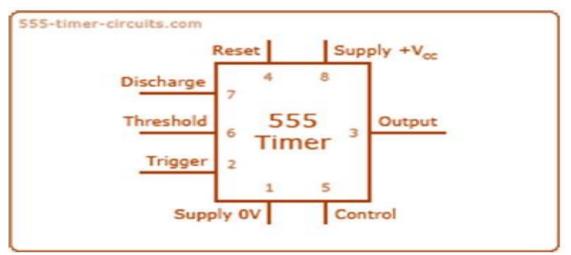

**Diagram 1: IC Timer Block Diagram**

The identified role of Upper comparator is to do a comparison of threshold voltage (linked at pin 6) with regards to +2/3 Vcc volt. Whilst the Lower Comparator undertakes the comparison of the voltage produced at pin 2 with regards to +1/3Vcc volts. In most aspects, the regulating input is not applied, hence this equalizes the alternating voltage to +(2/3)Vcc (Camenzid).

Comparator 1 with a threshold value (pin 6), the control value (pin 5). The frequencies from Comparator 2 is directed to in still the flip-flop in input S. anytime the prequalified voltage supersedes the adjustment voltage, the Comparator 1 will activate the flip-flop and rate high the output (. The greater output off the flip-flop when assigned to the central control unit of discharge transistor overlaps it and then draw off the charges in the transistors interconnected in the outside input (Pin7). The supplementary signal off the flip-flop enters pin 3.

Which is the described as the output. The present residual output in pin 3 is limited. These process will progress until Comparator 2 produces the flipflop.

There is no expected observable change in the flip-flop no matter how rapidly the input voltage will go below (2/3) VCC installed in the Comparator 1. The assumption remains that Comparator 1 might only push up the fli-flop's output. To alternate the final end of flip-flop to a lower degree, the voltage triggered by the inbuilt device must decrease at most not above +(1/3) VCC. When the course action mentioned above partakes, comparator 2 produces the flip-flop, pushing the output down to a lower degree(Everest). The low unit in the flip-flop regulates the discharge transistor setting it off and discharging other inputs in the favour of power amplifier which is set high on output.

www.ijera.com

The action progresses with the push of voltage on the trigger unit. Comparator 2 in this case operates by decreasing down casting the flip-flop to a low unit. The discussion here can be summed up that; in order to realize a low output in the functionality of timer 555, the energy inflicted bythe threshold unit must go beyond the control voltage or +(2/3) VCC. The action progresses to turning the discharge transistor in action. To upgrade the output off the timer, the voltage inside the trigger input must go down to +(1/3). This switches off the discharge transistor. A voltage may be transformed to direct the input in regulating the degree at which the off discharge partakes.

Sometimes a voltage may be asserted on the control unit to diversify the frequency at which the switching action takes place. When not functional, a 0.01 nf should be linked beneath pin 5 and regulated to alter any presence of noise which could result to false triggering. Fixing the reset (pin 4) on to a logic below the ceiling will switch high the flip-flop output. The discharge transistor will progress with its discharging action as the power amplifier goes low. This action persists until when the reset goes up. This gives room for synchronization or resetting of the circuits action. When inactive, reset should be interlinked to +VCC.

# The 555 timer Connections as A stable Multivibrators and its operation

This case elaborates the functionality of 555 timerA stableMultivibrators, how connections are undertaken within the circuit flow. Pin 1 is concealed; while pins 4 and 8 are cut short and fixed to produce +VCC, after which output (Vout) is switched off the pin3; pin 2 and 6 are cut short and affixed on the ground input via the capacitor C, pin 7 is produce +VCC via a resistor RA, and beneath

-Circuits

### **Astable Multivibrators Working**

To direct on how 555 timer stable Multivibrators operates, a circuit flow is presented in diagram below, this shows the internal operation of 555 timer IC (comprising of two Op Amps, an SR Flip Flop alongside the transistor affixed at the discharging input-pin 7). A wave trend from the output terminal (Vout-pin 3) is asserted on the right side of the circuit diagram as shown below.

### Monostable Multivibrators using a 555 timer

This part derives another critical implication of 555 Timers which is a Monostable Multivibrators. A system portrayed as the pulse distributing circuit having a single stationary and another single quasi-stationary terminal.Because there exists only a single state, the circuit is referred to as "Monostable Multivibrator"(Gafarov and Valehov). The period at which current alternates is derived by the RC connectivity affixed outside of the 555 Timer.

The stationary state output is proportionately zero or logically at the lowest level possible. The outside node discharging pulses assert forces which make the output higher or almost VCC. Absolutely after a proportionate time framework, the output particularly gets back to the stable position and maintain its low point up to a point where a trigger pulse is once more installed. The cycle then recycles again; this is because every moment a trigger pulse is used; the circuit ejects a single pulse. Therefore, referred in other terms as "one-shot Multivibrators"

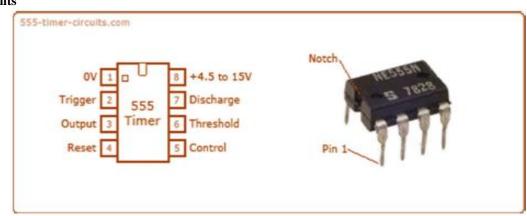

**Diagram 3: 555 Timer-Circuits**

The Timer IC 555's pin details are as follows according to Gafarov and Valehov:

PIN1: Ground Pin: interlinks to the 0V energy supply, each individual voltage is valued in line with the terminal.

PIN 2: Trigger terminal: The final trigger relies on the amplitude switched on external output pulse engaged to this pin. When an insignificant progressive pulse of amplitude above 1/3 VCC is employed to this terminal, the 555 timer voltage rises. The output maintains its high voltage provided the trigger output is maintained at lower level. If Pin 2 is below the ceiling and pin 6 as well, the output rises and remain stationary. While if pin6 rises and pin 2 drops, output decreases as pin 2 drops. This pin has a very huge impedance on 10 MΩ and will spur at a degree of about 1 μA.

PIN 3: Output: The output of the timer is valued here with regards to the laid platform. There are two forms upon which a load can be interlinked to the output terminal: either beneath pin3 and ground or beneath pin 3 and load of voltage + VCC. Whenever there is low output, the current streams alongside the structured load is zero whenever the output is minimum.

At this point, the load affixed beneath pin 3 and +VCC is referred to as the normally on load while when interlinked beneath pin 3 and ground is referred to as normally offload. Consequently, when the output is too huge the current through the load linked between pin 3 and + VCC is 0. The underlined current is referred to as the source current. The maximum quotation of sink or source current is up to 200 Ma. (pin 3 and 7 are constituents) rises (about 2 V minimal than rail) and LOW (about 0.5 V minimal than 0 V).

PIN 4: Reset input: There is possibility of resetting the timer by engaging a negative pulse on the pin. Any time the reset node is not active, the reset function terminal is affixed to +VCC to avoid any occurrence of false sparking. Reset pin is internally linked High through 100 K $\Omega$ , should be reset under the limit 0.8 v to regulate the IC node.

**Diagram 3: 555 Timer-Circuits**

PIN 5: Control voltage: The applicable voltage attached to the pin will alter the timing of the RC connectivity (somewhat considerably). The outside voltage applicable on this node alters the threshold as it triggers voltage. Therefore, by traversing a

voltage across the pin or by interlinking a pot within this pin and ground, the transmission width of the triggered wave-form can be diversified. When not engaged, the regulating pin must coordinate with a  $0.01\mu$  F Capacitor to alter any noise crisis.

**Diagram 4: Monostable Circuit**

PIN 6: Threshold input: at a point where the voltage across the pin surpasses or equals the threshold voltage 2/3 VCC, the end state of the timer drops (Everest). Means configuration of 2/3 of rail voltage to derive low output if pin2 is up. The based node has a very greater impedance which is almost 10 M $\Omega$  which will traverse with almost 0.2 A.

PIN 7: Discharge Pin. This pin is linked from inside across the transistor assembly Q. therefore, the moment the output is high Q is switched off and perform the function of open circuit on the external capacitor C linked over it. Consequently, whenever the output is limited, Q is automatically reassembled and so prevail as a short circuit, linking out the external capacitor C to ground(Izawa). For instance, emission pin drops where after, pin 6 spots 2/3 rail voltage however, pin 2 needs to be up.

In places where pin 2 is high and pin 6 will definitely be up or down compared to pin 7 which maintains the low state. Discharge or rather emission pin opens high and maintain this position where pin 2 sense 1/3 rail voltage while pin 6 is low. Pin 7 in conjunction to pin 3 are all inclusive in

transmission line. (Pin 7 is equivalent to pin 3 although pin 7 does not rise-instead it opens up. However, it gets down and get grounded to almost 200MA.

PIN 8: + VCC. The supply node of +5V + 18V is installed across this pin closer to the ground. But this is primarily 5V DC when in operation alongside the IC circuits.

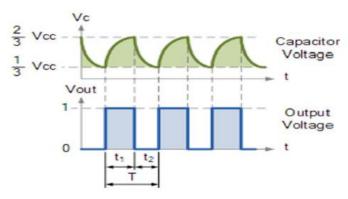

#### -Curves

The diagram below reviews the output wave fronts. The two critical measurements that one must realize from designed 555 Timer is ON and OFF Time. Literally, ON Time is the period in which the timer output Vout maintains its High position. Denoted as  $T_{HIGH}$ . OFF Time- is the period at which the timer output Vout is too LOW (Na. Which we denote as  $T_{LOW}$ . These functions, the ON and OFF Time are dependent on the  $R_A$ ,  $R_B$  and C in AstableMultivibrators (Nagaraj and Valehov). Hence we can get the preffered ON and OFF time on the timer output with actual calculation of  $R_A$ ,  $R_B$  and C factors.

**Diagram 5: Capacitor**

However, the Timer 555 has been applied in a diversified specific manner, it is therefore so contemporary on its waves transmission nodes, demanding somewhat a channel of current, and producing some noise transitory. This destruction will usually be attached next to ICs unwarranted emitting them. The 7555 is a CMOS model of the 555. Its latest current requisites are relatively lower compared to that of 555, and the 7555 does not compromise the power supply channels.

It is pin harmonious with the 555. So this CMOS model of the 555 Timer system need to be the foremost option when comes to 555 timer IC to be installed. IC Package: These ICs come in package form, either the inclusive metal form referred to as T package or the most prominent 8-pin DIP 'V' package(Vojtasek).

## **III. RECOMMENDATION**

This technology ought to be emulated especially in industries where circuits are applicable, it is recommendable as it is proven to be capable of producing a variety of output wave fronts when affixed with external RC connectivity. The device has also been tested and evident from the literature sources to have been in action since the implementation or the ICs. It is therefore recommendable that industries should adopt this instrument as it is more diversified and much adoptable with economical consumption of energy.

# IV. CONCLUSION

We have realized that Multivibrators in conjunction with CMOS Oscillators could be modified from discrete elements to enable the relaxation oscillation process to undertake, as this aids in creating a primary square wave output. The study posits that the name 555 Timers was derived from the aspect that there was three  $5K\omega$  resistors interlinked together within the device supplying a voltage divider connectivity beneath the supply voltage at pin 8 while on ground at pin 1 or the lower pin.

From the results the study presents that after pulse are triggered, the discharge output is switched OFF where the capacitor C inter-connected from outside begins charging to the top most degree through the resistor R. The maximum output pulse reaches its end upon the full charging of the capacitor to a level of 2/3 VCC. The internal process in line with the IC 555 in monostable system mode over the RC timing circuit is presented in diagram 2 and 3.

Consequently, the two critical measurements that has been realized from designed

555 Timer is ON and OFF Time where ON Time is the period in which the timer output Vout maintains its High position by Cass. Denoted as  $T_{HIGH}$ . OFF Time- is the period at which the timer output Vout is too LOW. Which we denote as  $T_{LOW}$ . These functions, the ON and OFF Time are dependent on the  $R_{A_c}R_B$  and C in Astable Multivibrators.

# WORKS CITED

- Camenzind, H. R. "Redesigning the Old 555 [Timer Circuit]." *IEEE Spectrum*, vol. 34, no. 9, Sept. 1997, pp. 80–85, https://doi.org/10.1109/6.619384.

- [2]. Cass, Stephen. "The Big Time: Build a Giant Version of the 555 Timer IC [Resources\_Hands On]." *IEEE Spectrum*, vol. 51, no. 3, Mar. 2014, pp. 25–26, https://doi.org/10.1109/mspec.2014.6745876.

- [3]. Everest, Frank. "The Characteristics and Use of the 555 Timer." *Electronics Education*, vol. 2000, no. 3, 2000, pp. 34–40, https://doi.org/10.1049/ee.2000.0051.

- [4]. Gafarov, Gadir, and S. E. Valehov. "Design of Stimulation Device of Biological Active Points Using 555 Timer." *Herald of the Azerbaijan Engineering Academy*, vol. 13, no. 4, 2021, pp. 113–20, https://doi.org/10.52171/2076-0515 2021 13 04 113 120.

- [5]. GONG, Jun, et al. "ICONE19-43092 SINGLE CHANNEL PULSE HEIGHT DISCRIMINATION CIRCUIT IMPLEMENTED by DUAL MONOSTABLE MULTIVIBRATOR." The Proceedings of the International Conference on Nuclear Engineering (ICONE), vol. 2011.19, no. 0, 2011, pp. \_ICONE1943–43, https://doi.org/10.1299/jsmeicone.2011.19.\_i cone1943\_33.

- [6]. Izawa, Jun. "Relaxation Oscillation with Tm:YLF Laser Using a Double Cavity in the Single-Longitudinal-Mode Oscillation." *Optical Engineering*, vol. 40, no. 3, Mar. 2001, p. 466, https://doi.org/10.1117/1.1347029.

- [7]. Nagaraj, K., and M. Satyam. "Multistage Monostable Multivibrator Using Load-Coupled Regenerative Feedback." *Electronics Letters*, vol. 17, no. 4, 1981, p. 159, https://doi.org/10.1049/el:19810112.

- [8]. Vojtášek, Stanislav. "Multivibrator with a Tunnel Diode." Applications of Mathematics, vol. 12, no. 4, 1967, pp. 268–77, https://doi.org/10.21136/am.1967.103101.