## **RESEARCH ARTICLE**

OPEN ACCESS

# An Efficient ASIC Design of RRC FIR Interpolation Filter for wireless Communication Applications

Priyanka Agrawal\*, Rajesh Mehra\*\*

\*(Department Of ECE, NITTTR, Chandigarh \*\* (Department Of ECE, NITTTR, Chandigarh) Corresponding Author: Privanka Agrawal\*

#### **ABSTRACT:**

The main objective of pulse shaping filter is to minimize intersymbol interference and shape the signal, In this paper an Application Specific Integrated Circuit (ASIC) is designed using Root Raised Cosine Interpolator Filter by employing multiplier less technique. The transposed direct form II structure of the filter is applied on the cadence platform which ultimately provides the reduced area and high speed. The HDL language is utilized for coding the provided filter specifications, thus the hardware complexity is reduced. The designed filter reduces the area by 40% which improves the hardware architecture. The maximum operating frequency is improved by 18% in comparison to previous work.

\_\_\_\_\_

Keywords: ASIC, RRC filter, area, Maximum frequency.

Date Of Submission: 10-01-2018

#### I. INTRODUCTION

The inspiration behind developing a single terminal device is software defined radio which has the capability of providing support to the multiple wireless communication standards like UMTS, WCDMA etc. As we know that different communication standards need different carrier to noise ratio, channel bandwidth, blocking and interference profile, and sampling rates to fulfill all these requirements one reconfigurable sample rate converter is required which can easily fulfill all specifications. Up sampler is widely used by interpolators while down sampler is used by decimator. These are used by the digital baseband signal in increasing or decreasing the sampling rate. Hence, the overlapping and interference effect is seen with the use of sample rate converter in the baseband signal. Therefore, to avoid this interference and overlapping effect any pulse shaping filter is used in shaping the signal. Due to high processing speed the interpolator utilise multirate filters applying less filter taps in parallel [1]-[5]. The transmitting or receiving of signals within a provided or particular channel bandwidth, increasing data transfer rate and to decrease BER is achieved by pulse shaping filters. The most suitable pulse shaping filter is root raised cosine filter (RRC) for the modern wireless communication systems like SDR, cell phones and set top box. RRC filter has high bandwidth limitation and inter symbol interference (ISI) rejection ratio criteria, which is why it is mostly used by multiple wireless standards like UMTS, WCDMA and IS-95. Date Of Acceptance: 27-01-2018

The ability of reducing the BER by rejecting timing jitter makes root raised cosine filter the best option to implement on ASIC platform [6]-[12].

As stated above Raised Cosine Filter is used to avoid interference, rectangular pulse infinite bandwidth is not considered in such cases. Rectangular pulse is passed through a low pass filter and we can observe the shape change from rectangular pulse to a pulse with no sharp edges and smoothly outlined. Therefore it is also known as pulse shaping process. The rectangular pulse exhibits non zero amplitude and smooth pulse exhibits few ripples prior and post pulse interval. The ripples can cause decoding of data in an incorrect manner at the receiver end as this ripple interferes with the pulses. The interference can be made minimum by maintaining a time domain shape and such a filter selection that provides the desired reduction in bandwidth. It finds its application in wireless devices and cellular phones for increasing speed, reducing power consumption and area [13]-[17].

$$\begin{split} F(w) &= \tau & 0 \leq w \leq c \\ (6) &= \tau \left\{ \cos^2[\tau(w\text{-}c)/4\alpha] \right\} & c \leq w \leq r \\ &= 0 & w > r \\ \end{split}$$

$$\begin{aligned} \textbf{Where} & \tau & \text{ is the pulse period} \\ \alpha & \text{ is roll off factor} \\ c & \text{ is equal to } \pi(1\text{-}\alpha)/\tau \\ r & \text{ is equal to } \pi(1\text{+}\alpha)/\tau \end{split}$$

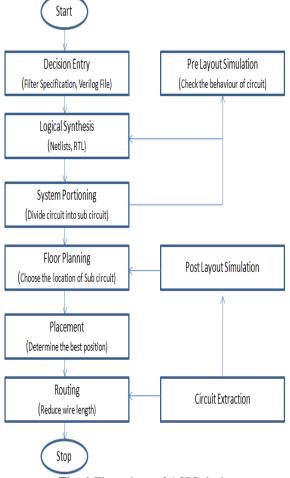

The availability of logic synthesis tools came in late 1990s. With help of these tools HDL descriptions

could be compiled into gate level netlists. Below are the steps for designing, these steps sometimes overlap in practical implementation:

Fig. 1 Flow chart of ASIC design

Requirement analysis is done to understand the required functions of the new ASIC. Using a HDL the goals are achieved and it starts with constructing the description of ASIC. Analogous process is utilized for writing the program using high level language. This method of designing is known as Register Transfer Level (RTL)

Functional verification is conducted to understand the suitability for purpose. Many techniques are included during the process, such as – emulation, formal verification, logic simulation, or creating software model equivalent, etc. Many methods are used and each technique has its own advantages and disadvantages RTL design is transformed into large collection of lesser level constructs which are called as standard cells using the logic synthesis process. Standard cell library which contains pre characterized collection of gates provides the constructs. Typically what happens is that standard cells are specific to the ASIC for the manufacturer. The result is called gate level netlist

which is nothing but collection of standard cells with required electrical connections. Now a placement tool is used process the gate level netlist, which places standard cells into final ASIC. Standard cells placement is attempted, however it is subjected to various constraints Physical placement of standard cell is taken by routing tool and is utilised to develop the electrical connection by using the netlist. This will help in developing a optimal solution. Physical Integrated Circuits can be produced by using the file output which is fed for creating a set of photo masks which enables the fabrication facility of semiconductor The final layout is used to calculate the capacitance and parasitic resistance. When there is a digital circuit further mapping is done into delay information, which in turn is used to identify the circuit performance, normally by static timing analysis. Further tests are done to ensure device works fine in case of extreme temperature, voltage, etc. For chip fabrication photomask information is provided to compete the process.

### **II. INTERPOLATOR**

Upsampling or interpolation adds zero in between the samples of original signal to increase the sampling rate, Now this signal with high sampling rate is provided as an input to the other system where this type of signal is needed. In a way upsampling provides distorted spectral images which is further removed by filtering. This motivated us to propose an interpolation factor of 8 for a 49 tap filter design.

#### III. MATLAB BASED INTERPOLATOR

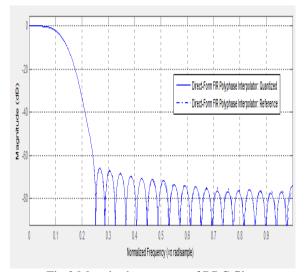

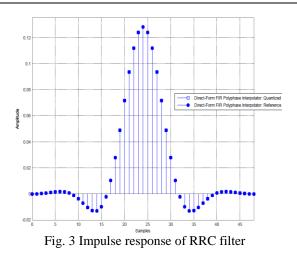

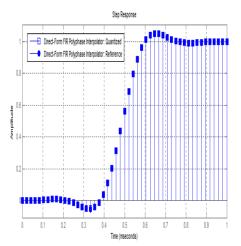

The impulse response of RRC filter decays in between 10 to 15 and 32 to 35 samples but after 35 samples it becomes stable the maximum variations is from 16 to 30 samples while the magnitude response decays and becomes stable at the end.

Fig 2 Magnitude response of RRC filter

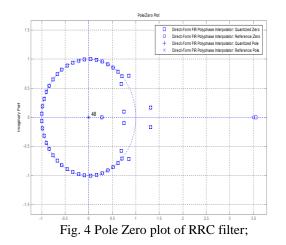

The unit circle is used to represent the pole zero plot, if all the poles lie inside the circle it represents the stable response, but if poles lie on the circumference of the circle then response is marginally stable and lastly if all the poles lie outside the circle then the response is unstable. As it can be clearly depicted from the fig 4. that the response is stable as all poles lie inside the circle.

Fig. 5 Unit step response of RRC filter

As it can be seen clearly that the unit step response shows variations or transient response till 0.7ms but after the 0.7ms the unit step response provides output as unity and thus the response becomes stable.

#### IV. ASIC SIMULATIONS

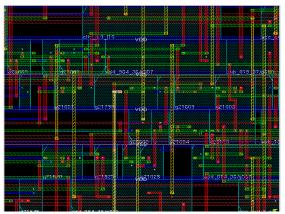

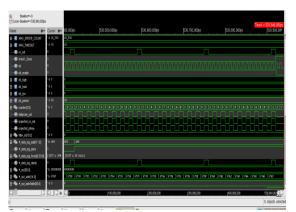

Fig 6. depicts the waveform produced before layout . Fig 7. depicts the laypout of the designed filter. Fig. 8 is achieved after floorplanning and routing.

Fig.6 Filter waveform before layout

Fig.7 Layout of Designed filter

Fig. 8 Filter waveform after layout

#### V. SYNTHESIS RESULTS

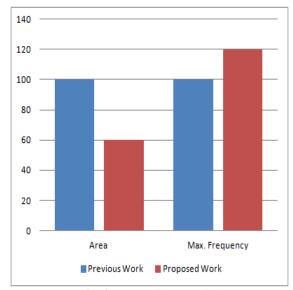

The ASIC design of 49 tap filter is compared with the previous work and the area is

found to be reduced by 40% and the maximum frequency is increased by 18%.

**Table I.** Comparison results on ASIC

| Parameter                 | Previous | Proposed |

|---------------------------|----------|----------|

|                           | work[1]  | work     |

| Area(mm <sup>2)</sup>     | 0.1617   | 0.0966   |

| Maximum<br>frequency(MHz) | 170      | 200      |

Fig. 9 Comparitive Analysis

#### VI. CONCLUSION

Thus the multiplier less technique used in implementing the RRC FIR interpolation filter reduces the hardware architecture and delay which is essential in wireless communication applications. The proposed transposed direct form II structure helps in minimizing the total number of nets and the connections between the devices. The architecture proposed in this paper is implemented using 180nm technology on ASIC platform. Therefore the optimization techniques makes operating frequency 18% more efficient and the area is reduced by 40% in comparison to previous work.

#### REFERENCES

- [1] Indranil Hatai, Indrajit Chakrabarti and Swapna Banerjee, "An Efficient VLSI Architecture of a Reconfigurable Pulse-Shaping FIR Interpolation Filter for Multistandard DUC," IEEE Transactions On Very Large Scale Integration Systems, Vol. 23, No. 6, pp. 1150-1154, June 2015.

- [2] P. K. Meher, S. Chandrasekaran, and A. Amira, "FPGA Realization of FIR Filters by Efficient and Flexible Systolization Using Distributed Arithmetic," IEEE Transactions on

Signal Processing, Vol. 56, No. 7, pp. 3009–3017, July 2008.

- [3] K.-H. Chen and T.-D. Chieueh, "A Low-Power Digit-Based Reconfigurable FIR Filter," IEEE Transactions on Circuits and Systems- II, Express Briefs, Vol. 53, No. 8, pp. 617–621, August 2006.

- [4] D. Shi and Y. J. Yu, "Design of linear phase FIR filters with high probability of achieving minimum number of adders," IEEE Transactions on Circuits and Systems- I, Regular Papers, Vol. 58, No. 1, pp. 126–136, January 2011.

- [5] Y. J. Yu and Y. C. Lim, "Optimization of Linear Phase FIR Filters in Dynamically Expanding Subexpressions Space," Circuits Systems, Signal Processing, Vol. 29. No. 1, pp. 65–80, June 2010.

- [6] R. Mahesh and A. P. Vinod, "New Reconfigurable Architectures for Implementing FIR Filters With Low Complexity," IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, Vol. 29, No. 2, pp. 275-288, February 2010.

- [7] J. Chandran, R. Kaluri, J. Singh, V. Owall, and R. Velijanovski, "Xilinx Virtex II Pro Implementation of a Reconfigurable UMTS Digital Channel Filter," in Proceedings IEEE Workshop Electronic Design, Test and Application, pp. 77–82, January 2004.

- [8] S.-J. Lee, J.-W. Choi, S. W. Kim, and J. Park, "A Reconfigurable FIR Filter Architecture to Trade off Filter Performance for Dynamic Power Consumption," IEEE Transactions on Very Large Scale Integrated (VLSI) System, Vol. 19, No. 12, pp. 2221–2228, December 2011.

- [9] I.Vinodhini and M.Thangavel, "Design of an Efficient Pulse Shaping FIR filter Architecture for Digital Up Converter," International Journal of Innovative Research in Science Engineering and Technology, Vol.4, Issue 6, pp. 507-513, May 2015.

- [10] Shahid Mehmood and Deepak Dasalukunte, "Hardware Architecture of IOTA Pulse Shaping Filters for Multicarrier Systems," IEEE Transactions on Circuits and Systems, Vol. 60, No. 3, pp. 733-742, March 2013.

- [11] Nicola Michailow, Maximilian Matte, Ivan Simoes Gaspar, Ainoa Navarro Caldevilla, Luciano Leonel Mendes, Andreas Festag and Gerhard Fettweis, "Generalized Frequency Division Multiplexing for 5<sup>th</sup> Generation Cellular Networks," IEEE Transactions On Communications, Vol. 62, No. 9, pp. 3045-3061, September 2014.

- [12] Rajesh Mehra and Swapna Devi, "Area Efficient and Cost Effective Pulse Shaping Filter for Software Radios," International Journal of Ad hoc, Sensor & Ubiquitous Computing (IJASUC), Vol. 1, No. 3, pp. 85-91, September 2010.

- [13] Monika Singh and Rajesh Mehra, "Design Analysis and Simulation of 25 TAP FIR Raised Cosine Filter," International Journal of Electrical & Electronics Engineering, Vol. 2, Spl. Issue 1, pp. 11-13, July 2015.

- [14] Monika Singh and Rajesh Mehra, "FPGA based RRC Filter Using Distributed Arithmetic Algorithm," International Journal of Advanced Information Science and Technology (IJAIST), Vol. 4, No. 7, pp. 122-126, July 2015.

- [15] Rajesh Mehra and S S Pattnaik, "Enhanced Resource Utilization in FPGA Based GSM Digital Up Converter," International Journal of Advanced Computing, Vol. 35, Issue 10, pp. 407-414, July 2012.

- [16] Rajesh Mehra, "FPGA Based Efficient WCDMA DUC for Software Radios," Cyber Journals: Multidisciplinary Journals in Science and Technology, Journal of Selected Areas in Microelectronics (JSAM), pp.8-13, December 2010.

- [17] Priyanka Agrawal, Rajesh Mehra and Monika Singh, "Implementation Cost and Performance Analysis of Pulse Shaping Filter," International Conference on Green Computing and Internet of Things (ICGCIoT), pp.1168-1172, October 2015.

International Journal Of Engineering Research And Applications (IJERA) Is **UGC Approved** Journal With Sl. No. 4525, Journal No. 47088. Indexed In Cross Ref, Index Copernicus (ICV 80.82), NASA, Ads, Researcher Id Thomson Reuters, DOAJ.

\_\_\_\_\_

Priyanka Agrawal. "An Efficient ASIC Design of RRC FIR Interpolation Filter for wireless Communication Applications." International Journal Of Engineering Research And Applications (IJERA), vol. 08, no. 01, 2018, pp. 81–85.

\_\_\_\_\_

www.ijera.com

DOI: 10.9790/9622-0801038185