# RESEARCH ARTICLE

# OPEN ACCESS

# Adiabatic Implementation on Full Adder Circuits

R.Swapna<sup>1</sup>, Shoban Mude<sup>2</sup>

<sup>1</sup> Guru Nanak Institute of Technology, E.C.E Dept., Hyderabad, India 2 Guru Nanak Institute of Technology, Asst .Prof, E.C.E Dept., Hyderabad, India

**Abstract:** In this paper we are going to design a adiabatic full adder using ECRL & PFAL logics and they are designed using DSCH & Micro Wind Software's. Thus the efficiency of the circuits are shown & compared using different nano meter technologies.

Keywords: Adiabatic, ECRL Adder, PFAL Adder, Full adder, Low Power Adders,

### I. Introduction

The main objective of this thesis is to provide new low power solutions for Very Large Scale Integration (VLSI) designers. Especially, this work focuses on the reduction of the power dissipation, which is showing an ever-increasing growth with the scaling down of the technologies. Various techniques at the different levels of the design process have been implemented to reduce the power dissipation at the circuit, architectural and system level.

Furthermore, the number of gates per chip area is constantly increasing, while the gate switching energy does not decrease at the same rate, so the power dissipation rises and heat removal becomes more difficult and expensive. Then, to limit the power dissipation, alternative solutions at each level of abstraction are proposed.

The dynamic power requirement of CMOS circuits is rapidly becoming a major concern in the design of personal information systems and large computers. In this thesis work, a new CMOS logic family called ADIABATIC LOGIC, based on the adiabatic switching principle is presented. The term adiabatic comes from thermodynamics, used to describe a process in which there is no exchange of heat with the environment. The adiabatic logic structure dramatically reduces the power dissipation. The adiabatic switching technique can achieve very low power dissipation, but at the expense of circuit complexity. Adiabatic logic offers away to reuse the energy stored in the load capacitors rather than the traditional way of discharging the load capacitors to the ground and wasting this energy.

This thesis work demonstrates the low power dissipation of Adiabatic Logic by presenting the results of designing various design/ cell units employing Adiabatic Logic circuit techniques. A family of full-custom conventional CMOS Logic and an Adiabatic Logic units for example, an inverter, a two-input NAND gate, a two-input NOR gate, a twoinput XOR gate a two-to-one multiplexer and a onebit Full Adder were designed in Mentor Graphics IC Design Architect using standard TSMC0.35  $\mu m$  Technology, laid out in Micro wind IC Station.

All the circuit simulations has been done using various schematics of the structures and postlayout simulations are also being done after they all have been laid-out by considering all the basic design rules and by running the LVS program. Finally, the analysis of the average dynamic power dissipation with respect to the frequency and the load capacitance was done to show the amount of power dissipated by the two logic families.

# II. Motivation

In the past few decades ago, the electronics industry has been experiencing an unprecedented spurt in growth, thanks to the use of integrated circuits in computing, Telecommunications and consumer electronics. We have come a long way from the single transistor era in 1958 to the present day ULSI (Ultra Large Scale Integration) systems with more than 50 million transistors in a single chip.

The ever-growing number of transistors integrated on a chip and the increasing transistor switching speed in recent decades has enabled great performance improvement in computer systems by several orders of magnitude. Unfortunately, such phenomenal performance improvements have been accompanied by an increase in power and energy dissipation of the systems. Higher power and energy dissipation in high performance systems require more expensive packaging and cooling technologies, increase cost, and decrease system reliability. None the less, the level of on-chip integration and clock frequency will continue to grow with increasing performance demands, and the power and energy dissipation of high-performance systems will be a critical design constraint.

For example, high-end microprocessors in 2010 are predicted to employ billions of transistors at clock rates over 30GHz to achieve TIPS (Tera Instructions per seconds) performance [1]. With this rate, high-end microprocessor's power dissipation is projected for each thousands of Watts. This thesis investigates one of the major sources of the power/energy dissipation and proposes and evaluates the techniques to reduce the dissipation.

Digital CMOS integrated circuits have been the driving force behind VLSI for high performance computing and other applications, related to science and technology. The demand for digital CMOS integrated circuits will continue to increase in the near future, due to its important salient features like low power, reliable performance and improvements in the processing technology.

The word *ADIABATIC* comes from a Greek word that is used to describe thermodynamic processes that exchange no energy with the environment and therefore, no energy loss in the form of dissipated heat. In real-life computing, such ideal process cannot be achieved because of the presence of dissipative elements like resistances in a circuit. However, one can achieve very low energy dissipation by slowing down the speed of operation and only switching transistors under certain conditions. The signal energy is stored in the circuit capacitances are recycled instead, of being dissipated as heat. The adiabatic logic is also known as *ENERGY RECOVERY CMOS*.

It should be noted that the fully adiabatic operation of the circuit is an ideal condition which may only be approached asymptotically as the switching process is slowed down. In most practical cases, the energy dissipation associated with a charge transfer event is usually composed of an adiabatic component and a non-adiabatic component. Therefore, reducing all the energy loss to zero may not possible, regardless of the switching speed. With the adiabatic switching approach, the circuit energies are conserved rather than dissipated as heat. Depending on the application and the system requirements, thisapproach can sometimes be used to reduce the power dissipation of the digital systems.

Here, the load capacitance is charged by a constant-current source (instead of the constant-voltage source as in the conventional CMOS circuits). Here, R is the resistance of the PMOS network. A constant charging current corresponds to a linear voltage ramp. Assume the capacitor voltage  $V_C$  is zero initially.

# III. 4. Adiabatic Logic Gate:

In the following, we will examine simple circuit configurations which can be used for adiabatic switching. Figure 3.2 shows a general circuit topology for the conventional CMOS gates and adiabatic counterparts. To convert a conventional CMOS logic gate into an adiabatic gate, the pull-up and the pulldown networks must be replaced with complementary transmission-gate (T-gate) networks. The T-gate network implementing the pull-up function is used to drive the true output of the gate, adiabatic while the T-gate network implementing the pull-down function drives the complementary output node. Note that all the inputs should also be available in complementary

form. Both the networks in the adiabatic logic circuit are used to charge-up as well as charge-down the output capacitance, which ensures that the energy stored at the output node can be retrieved by the power supply, at the end of each cycle. To allow adiabatic operation, the DC voltage source of the original circuit must be replaced by a pulsed-power supply with the ramped voltage output.

# IV. 3. Adiabatic Logic Types:

Practical adiabatic families can be classified as either PARTIALLY ADIABATIC or FULLY ADIABATIC [12]. In a PARTIALLY ADIABATIC CIRCUIT, some charge is allowed to be transferred to the ground, while in a FULLY ADIABATIC CIRCUIT, all the charge on the load capacitance is recovered by the power supply. Fully adiabatic circuits face a lot of problems with respect to the operating speed and the inputs power clock synchronization.

#### **ECRL-Efficient Charge Recovery Logic:**

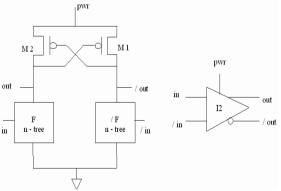

Efficient Charge–Recovery Logic (ECRL) proposed by Moonand Jeong [13], shown in Figure4.1,uses cross-coupled PMOS transistors. It has the structure similar to Cascode Voltage Switch Logic (CVSL) with differential signaling.

It consists of two cross-coupled transistors *M1* and *M2* and two NMOS transistors in the circuit.

An AC power supply *power* is used for ECRL gates, so as to recover and reuse the supplied energy. Both *out* and */out* are generated so that the power clock generator can always drive a constant load capacitance independent of the input signal .A more detailed description of ECRL can be found in. Full output swing is obtained because of the crosscouple PMOS transistors in both pre charge and recovers phases. But due to the threshold voltage of the PMOS transistors, the circuits suffer from the non-adiabatic loss both in the pre charge and recover phases. That is, to say, ECRL always pumps charge on the output with a full swing. However, as the voltage on the supply clock approaches to

So the recovery path to the supply clock to the supply clock is disconnected, thus, resulting in incomplete recovery.  $V_{tp}$  is the threshold voltage of PMOS transistor. The amount of loss is given as

$$EECRL = C|V_{tp}|^2/2$$

Thus, from Equation (4.2), it can be inferred that the non-adiabatic energy loss is dependent on the load capacitance and independent of the frequency of operation.

#### V. Positive Feedback Adiabatic Logic:

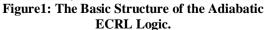

The partial energy recovery circuit structure named Positive Feedback Adiabatic Logic (PFAL)[15] has been used, since it shows the lowest energy consumption if compared to other similar families, and a good robustness against technological parameter variations. It is a dual-rail circuit with partial energy recovery. The general schematic of the PFAL gate is shown in Figure 4.3. The core of all the PFAL gates is an adiabatic amplifier, a latch made by the two PMOS M1-M2 and two NMOS M3-M4, that avoids a logic level degradation on the output nodes out and /out. The two n-trees realize the logic functions. This logic family also generates both positive and negative outputs. The functional blocks are in parallel with the PMOSFETs of the adiabatic amplifier and form a transmission gate. The two ntrees realize the logic functions. This logic family also generates both positive and negative outputs.

The two major differences with respect to ECRL are that the latch is made by two PMOSFETs and two NMOSFETS, rather than by only two PMOSFETs as in ECRL logic, and that the functional blocks are in parallel with the transmission PMOSFETs. Thus the equivalent resistance is smaller when the capacitance needs to be charged. The energy dissipation by the CMOS Logic family and Adiabatic PFAL Logic family can be Seen.

# VI. Adiabatic Full Adder using PFAL & ECRL

A partially adiabatic logic family PFAL onebit Full Adder block can be implemented as shown in the Figure 5.23 ( for SUM block) and Figure 5.24 (for OUTPUT\_CARRY) below, respectively.

#### Figure4: PFAL Sum Circuit

Figure5: PFAL Carry Circuit

Figure6: ECRL SUM Circuit

#### Figure7: ECRL Carry Circuit

The thesis primarily was centered on the look of low power CMOS cell structures, that is that the main contribution of this work. the look of low power CMOS cell structures uses totally complementary CMOS logic vogue Associate in Nursing an adiabatic PFAL logic vogue. The essential principle behind implementing numerous style units within the 2 logic designs is to check them with relation to the common power dissipated by all of them.

#### VII. Conclusion

A family of full-custom standard CMOS Logic Associate in adiabatic Logic units was designed DSCH and Micro wind& Digital Schematic and also the analysis of the common dynamic power dissipation with relation to the frequency and also the load capacitance was done. it absolutely was found that the adiabatic PFAL logic vogue is advantageous in applications wherever power reduction is of prime importance as in high performance battery-portable digital systems running on batteries like note-book computers, cellular phones and private digital assistants.

With the adiabatic approach, the circuit energies square measure preserved instead of dissipated as heat. revoking on the appliance and also the system needs, this approach are often wont to scale back the ability dissipation of the digital systems. With the assistance of adiabatic logic, the energy savings of up to seventy six guaranteed to ninety the concerns [15] are often reached.

#### Reference

- P.CHANDRAKASAN, S.SHENG, ANDR. W. BRODERSEN," Low Power CMOS Digital Design," *IEEE Journal of SolidstateCircuits*, Vol.27, No.04, pp.473-484, April 1999.

- [2]. H.J.M.VEENDRICK, "Short-circuit Dissipation of Static CMOS Circuitry and its Impact on the Design of Buffer Circuits," *IEEE JSSC*, pp. 468-473, August 1984.

- [3]. J. M.RABAEY, AND M.PEDRAM, "Low *Power Design Methodologies*," Kluwer Academic Publishers, 2002.

- [4]. M. HOROWITZ,T. INDENNAUR,AND R. GONZALEZ," Low Power Digital Design, "Technical Digest IEEE Symposium Low Power Electronics, San Diego, pp. 08-11, October 1994.

- [5]. T.SAKURAIANDA. R.NEWTON," Alpha-Power Law MOSET Modelandits ApplicationstoCMOSInverterDelayandother Formulas,"*IEEEJSSC*, vol.25, no. 02, pp. 584- 594, October 1990

- [6]. A.P.CHANDRAKASAN AND R.W.BRODERSEN, Low-power CMOS digital design, Kluwer Academic, Norwell,

Ma, 1995.

- [7]. SUNG-MOKANG AND YUSUF LEBLEBICI, CMOS Digital Integrated Circuits- Analysis and Design, McGraw-Hill, 2003.

- [8]. J. S. DENKER, "A Review of Adiabatic Computing," *Technical Digest IEEE Symposium Low Power Electronics*, San Diego, pp. 94-97, October 1994.

- [9]. T.GABARA," Pulsed Power Supply CMOS," *Technical Digest IEEE Symposium Low Power Electronics*, San Diego, pp. 98-99, October 1994.

- [10]. B.VOSSANDM.GLESNER, "ALowPowerSi nusoidalClock," *InProc.oftheInternational* Symposium on Circuits and Systems, ISCAS 2001.

- [11]. W.C.ATHAS, J.G.KOLLER, L.SVENSSON, "An Energy- Efficient CMOS Line Driver using Adiabatic Switching," Fourth Great Lakes symposiumon VLSI, California, March 2005.

- [12]. T. INDERMAUER AND M. HOROWITZ, "Evaluation of Charge Recovery Circuits and Adiabatic Switching for Low Power Design," *Technical Digest IEEE Symposium Low Power Electronics*, San Diego, pp. 102-103, October 2002.

- [13]. Y. MOON AND D.K.JEONG," An Efficient Charge Recovery Logic Circuit," *IEEE JSSC*, Vol. 31, No. 04, pp. 514-522, April 1996.

- [14]. A. KAMER, J. S. DENKER, B. FLOWER, et al., "2N2D-order Adiabatic Computation with 2N-2P and 2N-2N2P Logic Circuits," In Proc. of the International Symposium on Low Power design, Dana Point, pp. 191-196, 1995.

- [15]. A.BLOTTIANDR.SALETTI, "Ultralow-Power Adiabatic Circuit Semi-Custom Design," *IEEE Transaction son VLSI Systems*, vol. 12, no. 11, pp. 1248-1253, November 2004.

- [16]. S. YOUNIS, T. KNIGHT, "Asymptotically Zero Energy Split-Level Charge Recovery Logic. Proceedings Workshop Low Power Design, Napa Valley, California 1994, pp. 177-182.

- [17]. DRAGANMAKSIMOVIC´, G.VOJIN, OKLOBDŽIJA, BORIVOJENIKOLIC´ AND K.WAYNECURRENT, "Clocked CMOS Adiabatic Logic with Integrated Single-Phase Power-Clock Supply," *IEEE Transaction son VLSI Systems*, Vol.08, No. 04, pp. 460-463, August 2000.

- [18]. A. BLOTTI, S. PASCOLI, ANDR. SALETTI, "Sample Model for Positive Feedback Adiabatic Logic Power Consumption Estimation," *Electronics Letters*, Vol. 36, No. 2, pp. 116-118, Jan.

2000.

- [19]. C. HU, "Future CMOS Scaling and Reliability," *Proceedings IEEE*, Vol. 81, No.05, pp. 682-689, February 2004.

- [20]. W.C.ATHAS, L.SVENSSON, J.KOLLER, N.TZARTZANIS, ANDY.CHOU, "Low Power Digital Systems based on Adiabatic Switching Principles," *IEEE Trans. on VLSI Systems*, Vol. 2, No. 4, pp. 398-406, Dec. 1994.

- [21]. SAEDG.YOUNIS, "Asymptotically Zero Energy Computing Using Split-Level Charge Recovery Logic," PhD thesis, 1994.

- [22]. MICHAEL P. FRANK AND MARCOOTTAVI, "Energy Transfer and Recovery Efficiencies for Adiabatic Charging with various driving wave forms," Research Memo, 2006.

- [23]. KAUSHIKROY, SHARAT C. PRASAD, Low-Power CMOS VLSI Circuit Design, John Wiley & Sons, Inc, 2000.

- [24]. KAUSHIK ROY, YIBIN YE, Ultra Low Energy Computing using Adiabatic Switching Principle, ECE Technical Reports, Purdue University, Indiana, March, 1995.

- [25]. MOSIS: MOS Integration Service. Available online: <u>www.mosis.org</u>

# <sup>1</sup>R.swapna

Pursuing the M.tech degrees in VLSI-SD from Jawaharlal Nehru Technological University Hyderabad in 2013.Her area of interest is Digital electronics, signal and systems.

<sup>2</sup>Shoban mude is M. Tech post-Graduate of VLSI-SD from Guru Nanak Institute of Technology, Department of ECE, JNTU, Hyderabad. He obtained his B. Tech from S. R. Engineering college, Warangal. He has 4 years of teaching experience. He has published 3 conference papers, 1 journal and co-coordinator for the workshop ADOCS-13 in GNIT. His area of interest is control systems, communication systems and digital electronics.