# G Amitha, M Chandra sekhar, D Santosh, Venkatesh S / International Journal of Engineering Research and Applications (IJERA) ISSN: 2248-9622 www.ijera.com Vol. 3, Issue 2, March - April 2013, pp.1819-1824 An Area Efficient Reversible Multiplier Circuit Design By Using Low power Technique

G Amitha<sup>\*2</sup>, M Chandra sekhar<sup>#3</sup>, D Santosh<sup>#4</sup>, Venkatesh S<sup>#1</sup>

VITS group of institutions

## ABSTRACT

Power dissipation is one of the most important factors in the VLSI circuits design. By using reversible technique to reduce the power in the circuits. In this paper the reversible multiplier circuit design is also done by using low power technique called GDI and to compare the area and power of the multiplier in this technique with CMOS technique. In this paper a 4x4 reversible multiplier circuit is proposed with the design of two new reversible gates called ABC and GPS gates. The proposed multiplier was efficient to existing designs in terms of gate count, garbage inputs, and garbage outputs. The transistor level implementation of the proposed gates design by using Tanner tools.

Keywords - Reversible logic, garbage inputs, garbage outputs, gate count.

#### **I. INTRODUCTION**

Power dissipation is an important factor in VLSI design as modern logic circuits offer a great deal of computing power in a small footprint. The combinational logic circuits dissipate heat of KTln2 joules [1] for every bit of information erased during computation, where  $k = 1.3806505 \times 10-23 \text{J/K}$  is Boltzmann constant and T is the operating temperature in degrees at which the computation is carried out. Also, as Moore predicted that the number of transistors approximately doubles in every eighteen months and if this trend continues to hold, in the near future more and more energy will be lost due to the loss of information. Charles Bennett [2] showed that energy loss could be avoided or even eliminated if the computations are carried out in reversible logic and also proved that circuit built from reversible gates have zero power dissipation. Thus reversible logic appears to be promising in future low power design applications.

An efficient design in reversible logic should have the following features [3]: (a) use minimum number of reversible logic gates (b) should have less number of garbage outputs (c) less number of constant inputs and (d) minimization of quantum cost. Addition and multiplication operations are widely used arithmetic operations in many computations. High speed multiplier circuits are of particular interest in processor design.

Contribution: In this paper, we presented a reversible 4x4 multiplier with the design of new reversible gate called ABC Gate and GPS Gate. The proposed multiplier circuit is efficient compared to the existing designs in terms of gate counts, garbage outputs, constant inputs and quantum cost, and this design can be generalized to construct reversible nxn multiplier

Organization: The paper is organized into the following sections. Section 2 is an overview of basic reversible gates. The background work is described in section 3. Section 4 is about new reversible gate and the proposed multiplier design, results and discussions of the proposed design is presented in section 5 and conclusions are contained in section 6.

# **II. BASIC REVERSIBLE GATES**

Reversible logic gates are very much in demand for the future computing technologies as they are known to produce zero power dissipation under ideal conditions. A reversible circuit can be realized by using reversible gates only.

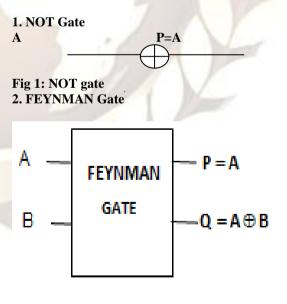

Fig 2: Feynman Gate

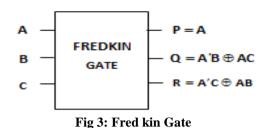

# **3.FREDKIN GATE**

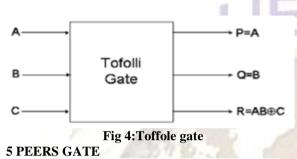

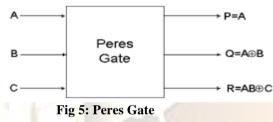

### **4**.TOFFOLI GATE

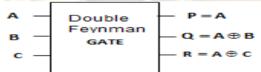

#### 6 .DOUBLE FEYNMAN GATE

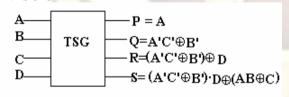

Fig 6: Double Feynman Gate 7 .TSG GATE

# **III. GDI TECHINQUE**

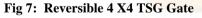

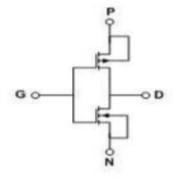

Gate-Diffusion-Input (GDI) method is based on the use of a simple cell as shown in figure .2. At a first glance the basic cell reminds the standard CMOS inverter, but there are some important differences: 1) GDI cell contains three inputs – G (common gate input of NMOS and PMOS), P (input to the source/drain of PMOS), and N (input to the source/drain of NMOS). 2) Bulks of both NMOS and PMOS are connected to N or P respectively, so it can be arbitrarily biased at contrast with CMOS inverter. It must be remarked, that not all the functions are possible in standard P-Well CMOS process, but can be successfully implemented in Twin-Well CMOS or SOI technologies.

#### Fig 8:GDI Basic cell

Table I shows how a simple change of the input configuration of the simple GDI cell corresponds to very different Boolean functions. Most of these functions are complex (6-12 transistors) in CMOS, as well as in standard PTL implementations, but very simple (only 2 transistors per function) in GDI design method.

Table I: Some logic functions that can be implemented with a single GDI cell

| Ν   | Р   | G | D      |

|-----|-----|---|--------|

| '0' | В   | А | AЪ     |

| В   | '1' | А | A'+B   |

| '1' | В   | А | A+B    |

| В   | '0' | А | AB     |

| С   | В   | А | A'B+AC |

| '0' | '1' | A | A'     |

#### IV. PROPOSED REVERSIBLE GATES 4.1(a) Proposed 3×3 Reversible ABC gate

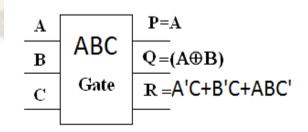

The logic diagram of the proposed new Reversible ABC gate is as shown in the Fig. 9. The corresponding truth table is shown in Table 1. ABC Gate which is a 3\*3 gate with inputs (A, B, C) and outputs P=A, Q= (A $\oplus$ B), R= A'C+B'C+ABC'.

Fig 9: Proposed 3×3 reversible ABC gate

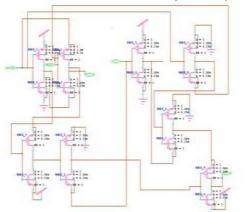

4.1(b) Implementation of ABC gate

Fig 10: Transistor level implementation of ABC gate

# 4.2. Implementation of GPS gate

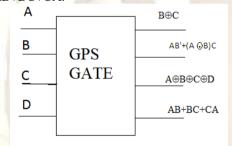

**4.2(a) Proposed 4×4 Reversible GPS gate** The logic diagram of the proposed new Reversible GPS gate is as shown in the Fig. 11 The corresponding gate truth table is shown in Table 2. GPS Gate which is a 4\*4 gate with inputs (A, B, C,D) and outputs P=B $\oplus$ C, Q=A, R= A $\oplus$ B $\oplus$ C $\oplus$ D, S=AB+BC+CA.

Fig 11: Proposed 3×3 Reversible GPS gate

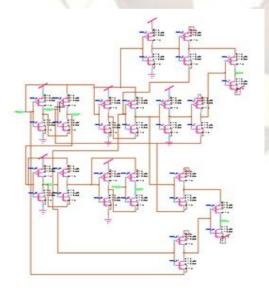

## 4.2(b)Implementaion of GPS gate

Fig 12: Transistor level implementation of GPS gate

# V: PROPOSED REVERSIBLE MULTIPLIER DESIGN

A  $4\times4$  Reversible multiplier has two parts..One is Partial Product term Generation (PPG) and other one is multi

Operand Addition circuit (MOA). The details of these two parts are following sections. The basic operation of  $4\times4$  multiplier as shown in figure 13. It consist of sixteen partial products of the form Xi . Yi , where I vary between 0 and 3

|       |       |       | X3<br>Y3 | X2<br>Y2 | X1<br>Y1 | X0<br>Y0 |

|-------|-------|-------|----------|----------|----------|----------|

|       |       |       | X3.Y0    | X2.Y0    | X1.Y0    | X0.Y0    |

|       |       | X3.Y1 | X2.Y1    | X1.Y1    | X0.Y1    |          |

|       | X3.Y2 | X2.Y2 | X1.Y2    | X0.Y2    |          |          |

| X3.Y3 | X2.Y3 | X1.Y3 | X0.Y3    |          |          |          |

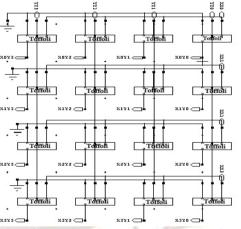

7776757473727170F Fig 13: The basic operation of a 4×4 multiplier5..1 Partial product term generation (PPG)PPG circuit using Toffoli gate is as shown in figure

14.Here 16 Toffoli gates are used to generate sixteen Partial products as shown in figure 13.

Fig 14: Partial product term generation circuit by using TG reversible gate

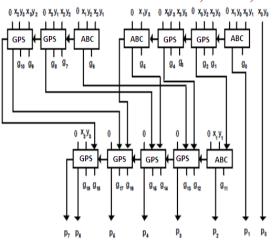

#### 5.2 Multi Operand Addition circuit(MOA)

The addition of partial products using new proposed gates called ABC and GPS gates is as shown in figure 15.The basic cell for a such a multiplier is full adder using GPS gate with here inputs and one constant input, two garbage outputs and half adder using ABC gate with two inputs and one constant output, one garbage output. The proposed multiplier uses eight GPS gates and four ABC gates, Sixteen Toffolli gates for partial product terms generation.

Fig15: Proposed 4×4 reversible multiplier

# VI.RESULTS AND DISCUSSIONS

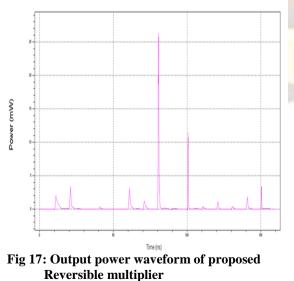

The simulation results of the multiplier as shown in figure 16 and figure 17.These two figures shows the voltage and power of the proposed reversible multiplier.

# 6.1 Simulation results of proposed Reversible multiplier

#### Fig: 16 Voltage wave form of proposed reversible Multiplier

# 6.2Comparison of CMOS and GDI techniques

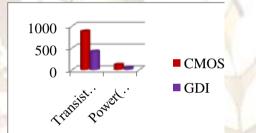

In proposed reversible multiplier the output power is reduced up to 62.61% by using GDI technique when compared to CMOS and the transistor count is also reduced by using GDI technique when compared to CMOS. The transistor count reduced means the area of the circuit is reduced.

The comparison results as shown in table-2

**TABLE-2** Comparison of CMOS and GDI

| Parameter/<br>Technique  | CMOS | GDI |

|--------------------------|------|-----|

| Number<br>of transistors | 880  | 416 |

| Power(µw)                | 115  | 43  |

# Fig 18: Comparison of CMOS and GDI techniques

# 6.3 Comparison of existing and proposed reversible multiplier circuits

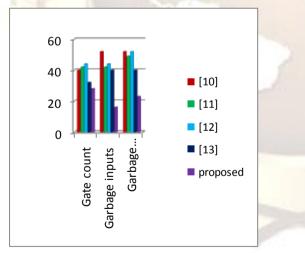

**Gate Count/Hardware Complexity:** one of the major factors of a circuit is measured in terms of number of gates. It can be proved that the proposed circuit is better than the existing approaches in terms of hardware complexity. In [10], the total number of reversible gates required is 40, [11] requires 42, in [12] total number of gates required is32.Theproposed design requires 28 gates. Therefore, the proposed design is better than existing design approaches in terms gate count.

**Garbage Inputs:** Number of constant inputs is one of the main factors in designing a reversible logic circuit. The input is used as a control input by connecting to logic low or high to get function at the output is called garbage input. The proposed design require 16 garbage inputs, but the existing designs[10], [11], [12] and[13] requires52, 42,44 and 40 respectively. So it clearly shows that the proposed design is better than existing designs in terms of garbage inputs.

**Garbage Outputs:** the output of the reversible gate that is not used as a primary input or as input to the other gates is referred as garbage output. Optimizing garbage outputs is one of the other main constraints

in designing reversible logic logic circuit. The proposed reversible multiplier circuit produces 23 garbage outputs, but the design [10], [11],[12] and [13] produces 52, 49,52 and 40 respectively. Therefore, it is clear that proposed design is better that the existing designs in terms of number of garbage outputs.

# Evaluation of the proposed reversible multiplier circuit:

The proposed reversible multiplier is more efficient compare to existing designs presented by [10], [11], [12] and [13].This can be comprehended easily with the comparison results as shown in table-3

TABLE-3 comparison of existing and proposed reversible multiplier circuit

| Multiplier/<br>parameter | Gate<br>count | 0  |    |

|--------------------------|---------------|----|----|

| [10]                     | 40            | 52 | 52 |

| [11]                     | 42            | 42 | 49 |

| [12]                     | 44            | 44 | 52 |

| [ [13]                   | 32            | 40 | 40 |

| proposed                 | 28            | 16 | 23 |

Figure19 shows the difference between existing and proposed multiplier designs in terms of gate count, garbage inputs and garbage outputs. So it clearly shows the proposed reversible circuit is more efficient when compared to existing designs.

Fig 19 Comparison of existing and proposed reversible multiplier designs

# VII CONCLUSIONS

In this paper the proposed  $4\times4$  reversible multiplier is designed with two new proposed gates called ABC and GPS. These two gates are useful in design of multi operand circuit (MOA). The Toffolli gate(TG) is useful in partial product term generation circuit(PPG).The results clearly shows that the number of gates , number of garbage inputs and number of garbage outputs are less in proposed reversible multiplier circuit compared to existing design approaches. In this paper the proposed reversible multiplier designed by using GDI technique and compares the area and power of the multiplier with the CMOS technique. These results shows the GDI is the best low power technique when compare to CMOS technique.

# REFERENCES

- [1] RLandauer,1961."*Irreversibility and Heat Generation in the Computational Process*". IBM Journal of Research and Development, vol. 5, no. 3, pp. 183-191.

- [2] C H Bennett, 1973. "*Logical Reversibility* of *Computation*".IBM Journal of Research and Development, vol. 17, no. 6, pp. 525-532.

- [3] Kerntopf P, M A Perkowski and M H A Khan, 2004, "On Universality of General Reversible Multiple Valued Logic Gates". Proceedings of the Thirty Fourth IEEE International Symposium on Multiple valued Logic, pp. 68 – 73.

- [4] Richard P Feynman, 1985. "Quantum Mechanical Computers". Optics News, vol. 11, issue 2, pp. 11-20.

- [5] T Toffoli, 1980. "*Reversible Computing*".Technical Memo MIT/LCS/TM-151, MIT Lab for Computer Science.

- [6] Edward Fredkin and Tommaso Toffoli, 1982. "Conservative Logic". International Journal of Theoretical Physics, vol. 21, Synthesis of Multiple Outputs Boolean Functions pp. 219-253.

- [7] A Peres, 1985, *"Reversible Logic and Quantum Computers"*. International Journal on Physical Review a General Physics, vol. 32, no. 6, pp. 3266–3276.

- [8] William N. N. Hung, Xiaoyu Song, Guowu Yang, Jin Yang, and Marek Perkowski, 2006. "Optimal Using a Set of Quantum Gates by Symbolic Reachability Analysis". IEEETransactions on Computer-Aided Design of Integrated Circuits and Systems, vol. 25, no. 9, pp. 1652-1663.

- [9] H Thapliyal and N Ranganathan, 2009. "Design of Efficient Reversible Binary Subtractors Based on a New Reversible Gate". Proceedings of the IEEE Computer Society Annual Symposium on VLSI, pp. 229-234.

- [10] H R Bhagyalakshmi and M K Venkatesha, 2010. "An Improved Design of a Multiplier using Reversible Logic Gates". International Journal of Engineering Science and Technology, vol. 2(8), pp. 3838-3845.

- [11] Rigui Zhou, Yang Shi, Jian Cao and Huian Wang, 2010. "Comment on Design of a Novel Reversible Multiplier Circuit using HNG Gate in Nanotechnology". World Applied Sciences Journal, vol. 10(2), pp. 161-165.

- [12] M S Islam, M M Rahman, Z Begum and M Z Hafiz,2009. "Low Cost Quantum Realization of Reversible Multiplier Circuit" Information Technology Journal, vol. 8(2), pp. 208-213.

- [13] Rangaraju HG, Akash Babu, Muralidhara KN, "DesignAnd Optimization Of Reversible Multiplier Circuit". International journal of Computer applications (0975-08885

- [14] Eitan V.Shaaly"CMOSlekage and power reduction in transistors and circuits: Process layout and considerations" International journal of low power electronics and applications ISSN2079-9268

- [15] Arkadiy Morgenshtein, AlexanderFish and Israel A.Wargan, "Gate Diffusion Technique(GDI) for low power design of digital circuits analysis and charecterization" IEEE transactions' on VLSI systems,