### N. Kiran babu, Asst.Prof. M.siva kumar / International Journal of Engineering Research and Applications (IJERA) ISSN: 2248-9622 www.ijera.com Vol. 3, Issue 2, March - April 2013, pp.556-558 Test Sequence Generation of Random Single Input Change (RSIC) Based on Counter

## N. Kiran babu<sup>1</sup>, Asst.Prof. M.siva kumar<sup>2</sup>

<sup>1</sup> (M. Tech student, Department of Electronics and Communication Engineering, K L University, Vaddeswaram, Guntur Dt.)

<sup>2</sup>(Assoc. Prof, Department of Electronics and Communication Engineering, K L University, Vaddeswaram, Guntur Dt.)

#### ABSTRACT

In any VLSI circuit, power consumption is very important factor that should be taken into Generally, dynamic power consideration. consumption is more dominant when compared to that of static. To reduce the internal switching activity rate of the circuit under test (CUT), we can recombine testing vector to raise the correlation between testing vector. Random Single Input Change (RSIC) test theory is proposed, which optimize the switching activity of circuit-under-test and then result in decrease of test power consumption. It is suitable for BIST of digital VLSI especially. The proposed circuit is simulated in DSCH and Cadence- Virtuso. The results obtained in various tools are presented in this paper.

**Keywords** – Built-in-self-test, Cadence Virtuso software, Test pattern generator, low power testing.

#### I. INTRODUCTION

In recent years, with the development of very large-scale integrated circuit and system of chip (SoC), test of integrated circuits faces more and more difficulties; especially power consumption under testing pattern is greatly higher than that under working pattern, this problem attracts more attention. Following the continuous improvement of IC working frequency integration and complex, the power consumption of IC rapidly increases. Taking Intel processor as example, its biggest power consumption increases by 100% each four years.

Especially under the technology of deep sub-micron, the width of line is smaller and smaller, so the electronic density requirement to line becomes stricter. Electric moving speed becomes faster with the rise of temperature, which leads to increase the invalid rate of connection line, thus reducing the

reliability of the whole circuits. The temperature rise caused by high power consumption also lowers the moving rate of charge carrier, which increases the switching time of transistor, then reduces the performance of system.

# II.CMOS CIRCUIT ENERGY AND POWER CONSUMPTION

Power consumption in CMOS VISL is divided into two kinds static and dynamic.

#### **2.1 STATIC:**

Static power consumption is mainly produced by leak current. The structure of CMOS circuit is complementary and symmetry, only one tube is on at the same time, leak current is small, so static power consumption isn't the major part of system power consumption.

#### 2.2DYNAMIC

Dynamic power consumption is from short circuit current generated by '0/1'or '1/0'switching of component, and from power consumption produced by discharging or charging of load capacitance. Generally speaking, dynamic power consumption is the main source of circuit power consumption.

In CMOS circuit, average dynamic power consumption  $P_d$  of one CMOS logical gate can be expressed as[4]:

$P_d = \alpha f C_L V_{DD}^2 \tag{1}$

In this formula,  $\alpha$  is the rate factor of switching activity of reaction circuit, f is working frequency,  $C_L$  is output node of the whole load capacitance,  $V_{DD}$  represents mains voltage.

From formula (1) we can know dynamic power consumption in CMOS VLSI mainly depends on three parameters: mains voltage  $V_{DD}$  clock frequency f and rate factor a which reflects the switching activity rate of node. Through reducing mains voltage  $V_{DD}$  and clock frequency f, it may drop power consumption, but this way also lowers the performance of circuit. So it's a main technology to reduce power consumption through lowering the switching activity.

#### **III. INDENTATIONS AND EQUATIONS**

There is only one different vector called "Random Single Input Change" between two adjoining random vectors. It has high correlation between Random Single Input Change testing vector, which can realize low power consumption during testing through dropping switching activity rate of under-test circuit. Documentary [5]

#### N. Kiran babu, Asst.Prof. M.siva kumar / International Journal of Engineering Research and Applications (IJERA) ISSN: 2248-9622 www.ijera.com Vol. 3, Issue 2, March - April 2013, pp.556-558

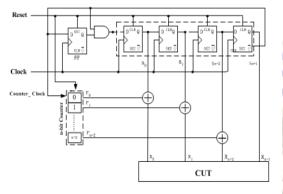

researches the theory of single input change, it proves single input change vector can be more effective than random vector to reduce the switching activity rate of under-test-circuit node. Figure 1 shows circuit design method of RSIC sequence generated by logical circuit, which consists of n digits shift register (n-1) counter and several two input XOR.

Figure 3.1. RSIC TESTING GENERATOR First of all, shift register SR is initiated to (0, 0, 0, ..., 0), flip-flop is set to "1"by enable signal, FF and SR are controlled by common testing clock signal, SR produces testing vector in the (n+1) clock cycle: {(0,0,0,...,0),(1,0,0,...,0), (1,1,1,...,0), ...(1,1,1,...,1)}. When next signal is started, the first level of SR is set to "o" by "or" gate, after n clock pulses, the output of SR is {(0,1,1,...,1),(0,0,1,...,1),(0,0,0,...,1), ...(0,0,0,...,0)}, at

last, it recycles above process continuously.

**IV. SIMULATION RESULTS**

After initiation, the output of counter stays stable during (2n+1) clock period, but SR produces (2n +1) different testing vector. Affected by signal counter-clock, SR makes "XOR calculation of corresponding digit", which can produce (2n+1)single input change (SIC) testing vector. It can be used to test power consumption for integrated circuit.

When CUT Generating output '1':

When CUT Generating output '0':

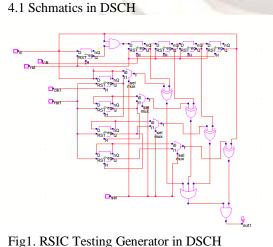

In this DSCH tool, the correct path is displayed in one colour and the path with fault is displayed in another colour so that we can differentiate faulty paths easily.

#### **3.2 Schematics in Cadence**

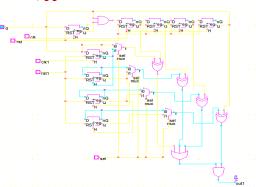

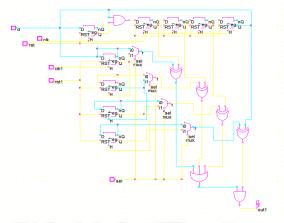

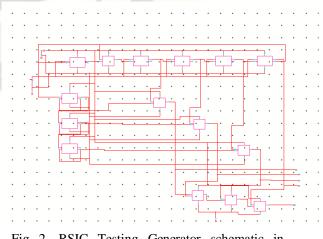

In cadence, to create the entire schematic, initially it is necessary to create symbols for each and every block in the circuit. In RSIC Testing Generator, the main blocks that exist are D-Flip flop, Multiplexer, 2- input XOR gates, 2- input AND gates, 3- input OR gates. So, if we create schematics for those blocks then the respective symbols can be instantiated in the main module.

Fig 2. RSIC Testing Generator schematic in Cadence-Virtuso

#### N. Kiran babu, Asst.Prof. M.siva kumar / International Journal of Engineering Research and Applications (IJERA) ISSN: 2248-9622 www.ijera.com Vol. 3, Issue 2, March -April 2013, pp.556-558

The following are the output waveforms in Cadence:

Fig3. Output waveform in cadence

#### **Power Dissipation Values**

D- Flip flop : 935.898 pW 2- input XOR gate : 1.27603 nW 2- input OR gate : 32.4249 pW 2- input AND gate : 653.021 pW 2- input NAND gate : 187.583pW RSIC circuit : 213.034 mW Delay in RSIC circuit is : 10.59E-9

Power dissipation values for the each module can be known while generating its transient analysis. Log file of the particular module contains its power dissipation value.

#### **V. CONCLUSION**

In this paper mainly deals with generation of random testing sequence using single input change based on counter. The research of this paper indicates single input change testing sequence has higher correlation than multi-input change. During testing, it can reduce switching activity rate  $\alpha$  of under-test-circuit internal node in order to lower power consumption. This circuit is implemented in DSCH, Cadence and its results are mentioned in the paper.

#### ACKNOWLEDGEMENTS

I am grateful to **Asst.Prof.M.Siva Kumar, K L University** for his constant encouragement and I whole heartedly thank him for his support in completion of this paper successfully. I would like to express my heartfelt thanks to my beloved parents for their blessings and their wishes that helped me in successful completion of this report.

#### REFERENCES

- BONHOMME Y. Test Power: A Big Issue in Large SOC Design. Proceedings of the First IEEE International Workshop on Electronic Design, Test and Application DELTA'02, 2001,447-449

- 2) F CORNO, P PRINETTO, M REBAUDENGO, et al. A Test Pattern Generation Methodology for Low Power Consumption. IEEE VTS, 1998: 453-457

- 3) ARNAUD VIRAZEL, HANS-JOACHIM WUNDERLICH, High Defect Coverage with Low-Power Test Sequence in a BIST Environment. IEEE Design &Test of Computer, 2002, 18 (6):44-52.

- 4) GAN Xue-wen, Mo Bang-xian, A Overview of Low-Power Digital CMOS Design, Micro-electronics, 2000, 30(8): 26(2):5-7.

- 5) Yi Wang, Xing-hua Fu, Research on A Low Power Consumption for Random Single Input Change Test Theory. Microelectronics and Computer [J], 2009, 26(2):5-7.

- 6) IOANNIS VOYIATZIS, ANTONIS PASCHALIS. An Efficient Built-in Self Test Method for Robust Path Delay Fault Testing. JORNAL OF ELECTRONIC TESTING: Theory and Application 8,219-222