# D.Dayakara Reddy, S.Karunakar Reddy / International Journal of Engineering Research and Applications (IJERA) ISSN: 2248-9622 www.ijera.com Vol. 3, Issue 1, January-February 2013, pp.048-051 FPGA Implementation of QAM Transmitter and Receiver

# D.Dayakara Reddy, S.Karunakar Reddy

VLSI SYSTEM DESIGN

Aurora's Technological & Research Institute Hyderabad, India Assoc. Professor Aurora's Technological & Research Institute Hyderabad, India

Abstract—The FPGA technology has been playing a considerable role in Rportable and mobile communication. This is due to the features of flexibility. accuracy and configurability in designing and Implementation. The project presents a complete design for QAM Transmitter and Receiver based on the Spartan 3e FPGA kit. The implemented system can be used in typical wimax system and any other communication systems. The carrier synchronization and timing synchronization issues are covered in the implementation. The transmitter of QAM consists of data sampler, phase accumulator, symbol mapper, NCO. The receiver of OAM consists of phase locked loop, symbol demapper, clock distributer. Modelsim Xilinx edition(MXE) will be used for simulation and functional verification. Xilinx ISE will be used for synthesis, and bit file generation. Xilinx FPGA board will be used for testing and demonstration of the implemented system.

**keywords:** FPGA design, Carrier Synchronization, Symbol Recovery, QAM modulation;

## I INDRODUCTION

Quadrature Amplitude Modulation or QAM is a form of modulation which is widely used for modulating data signals onto a carrier used for radio communications. It is widely used because it offers advantages over other forms of data modulation such as PSK, although many forms of data modulation operate along side each other.

Quadrature Amplitude Modulation, QAM is a signal in which two carriers shifted in phase by 90 degrees are modulated and the resultant output consists of both amplitude and phase variations. In view of the fact that both amplitude and phase variations are present it may also be considered as a mixture of amplitude and phase modulation.

### I Analogue and Digital QAM

Quadrate amplitude modulation, QAM may exist in what may be termed either analogue or digital formats. The analogue versions of QAM are typically used to allow multiple analogue signals to be carried on a single carrier. For example it is used in PAL and NTSC television systems, where the different channels provided by QAM enable it to carry the components of chroma or colour information. In radio applications a system known as C-QUAM is used for AM stereo radio. Here the different channels enable the two channels required for stereo to be carried on the single carrier.Digital formats of QAM are often referred to as "Quantised QAM" and they are being increasingly used for data communications often within radio communications systems. Radio communications systems ranging from cellular technology through wireless systems including WiMAX, and Wi-Fi 802.11 use a variety of forms of QAM, and the use of QAM will only increase within the field of radio communications.

## A. Digital / Quantised QAM basics

Quadrature amplitude modulation, QAM, when used for digital transmission for radio communications applications is able to carry higher data rates than ordinary amplitude modulated schemes and phase modulated schemes. As with phase shift keying, etc, the number of points at which the signal can rest, i.e. the number of points on the constellation is indicated in the modulation format description, e.g. 16QAM uses a 16 point constellation.

When using QAM, the constellation points are normally arranged in a square grid with equal vertical and horizontal spacing and as a result the most common forms of QAM use a constellation with the number of points equal to a power of 2 i.e. 2, 4, 8, 16.... By using higher order modulation formats, i.e. more points on the constellation, it is possible to transmit more bits per symbol. However the points are closer together and they are therefore more susceptible to noise and data errors.

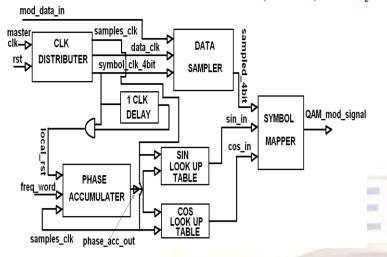

## II QAM TRANSMITTER DESIGN

Block diagram of QAM modulator is given above every block is explained below in detail. Clk\_distributor the inputs for the clock generation module is reset and master clock of 50Mhz and the outputs are sample\_clk, data\_clk and symbol\_clk. The sample\_clk is same as the master\_clk. The clock generation module consists of 10 bit counter. In the counter  $8^{th}$  bit value gives the output of data\_clk and the  $10^{th}$  gives the output of symbol\_clk . The data\_clock will be at active low for 256 clock pluses and for other 256 clock pluses will be in active high to complete one cycle. Symbol\_clk will be at active low for 1024 clock pluses and for other 1024 clock pluses will be in active high to complete one cycle

### D.Dayakara Reddy, S.Karunakar Reddy / International Journal of Engineering Research and Applications (IJERA) ISSN: 2248-9622 www.ijera.com Vol. 3, Issue 1, January-February 2013, pp.048-051

Rst is used to clear or reset module, data\_clk will be four times faster then symbol\_clk\_4bit When rst is active high then left shift register will be cleared, if rst is active low with raising edge of data\_clk then data\_in will be forced on to the LSB bit of left shift register. Left shift register will be shifter one bit. Raising edge of symbol\_clk\_4bit then left shift register will be reflected on the output sampled\_4bit.

Clk is used for synchronication and rst is used to clear two registers that are phase increment registrer and phase register. The phase increment register stores the instantaneous phase\_inc\_word that is fed to a 8 bit adder as one of its input. The other input for adder is phase register output. The phase register holds the instantaneous phase for each clock pulse (i.e adder output). The accumulated phase also is also 8 bits, which limits the maximum phase by 1111111, and addition by 1 to maximum value causes the phase to become 00000000

#### SIN AND COS LUT'S

According to the address given the predefined data stored in 8 bit rom will reflected on the output pin Amp\_Bits. This is expected and desired since the Look Up Tables are programmed to consider 255 as highest phase value and phase increment by one results next cycle of waveform. Since 8 bits are used to represent the  $0^{\circ}$  to  $360^{\circ}$  the increment in digital phase value by one causes effective increment of  $1.40625^{\circ}$  (results by dividng  $360^{\circ}$  with 256 maximum possible combinations of 8 bits). This also implies that outputs can't have more that 256 samples for one cycle.

### SYMBOL MAPPER

This incremented phase is multipled with sin and cos for sin\_lut and cos\_lut respectively. The resultant amplitude will be saved in the 8 bit Rom block. So according to address that will give ampltude of sin or cos signal by using this LUT's Sampled\_4bit data is loaded in to a tempary register there  $0^{th}$  bit and  $1^{st}$  bit are assumed as I bits and  $2^{nd}$

and 3<sup>rd</sup> bit are asumed as Q bits, these I bits and Qbits are assumed as address to 3 bit Rom block's in this according to Rom address data in that address will be given to the next block called as multipler's. I bits are multipled with cos\_in bits and Q bits are multipled with sin\_in bits than resultant output's of the multipler section will be added which generates the final output as QAM\_mod\_signal.

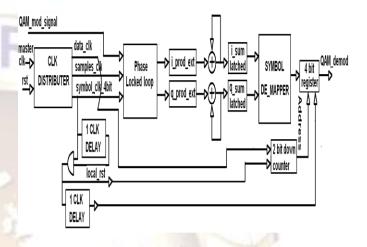

## III QAM RECEIVER DESIGN

The system generator library provides a demo for QAM baseband demodulator which consists of two main blocks: Carrier recovery and Symbol demapper. Fast computing techniques using CORDIC is employed to correct the phase error. The adaptive algorithm does work to minimize errors. However, because of these features, this design cannot be applied to deep fading channels phenomenon.

QAM\_mod\_signal samples\_clk Multiplie PFi Filter PID LOOK UP ATAN Controlle PHASE freq\_word block ACCUMULATER PFir Multipli Filter phase acc ou symbol clk 4bit VRef 1 CLK DELAY

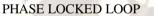

Phase locked loop is used to correct the signal at demodulator it's plays a key role in demodulation. The carrier recovery can be done by using phase locked loop. It consists of phase accumulator. Phase accumulator is the combination of phase register and phase increment register. The phase increment register stores the instantaneous phase\_inc\_word that is fed to a 8 bit adder as one of its input. The other input for adder is phase register output. The

## D.Dayakara Reddy, S.Karunakar Reddy / International Journal of Engineering Research and Applications (IJERA) ISSN: 2248-9622 www.ijera.com Vol. 3, Issue 1, January-February 2013, pp.048-051

phase register holds the instantaneous phase for each clock pulse (i.e adder output). The accumulated phase also is also 8 bits, which limits the maximum phase by 11111111, and addition by 1 to maximum value causes the phase to become 00000000.

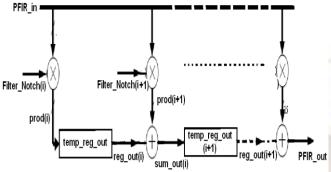

PFIR module:

The package created which consist of the filter coefficients will be utilized by calling the package in to program; PFIR structure is shown in above figure. Input is taken as PFIR\_in and is given to a multiplier in a loop and another input to multiplier is the filter coefficient (i) stored in the PFIR package. Result generated by the multiplier will be added with another multiplier in the loop (i+1). Loop will be running till last coefficient is multiplied and result is reflected on to output signal PFIR\_out.

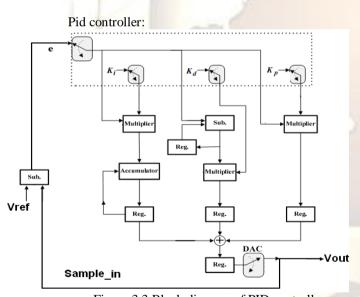

Figure 3.3 Block diagram of PID controller The output of the system is taken as input (i.e sample\_in) of pid controller as that is compared with vref to generate error signal. Pid control has three section that is integration section, differentiation section and proportional section. In Proportional section gain  $K_p$  is multiplied by error and produces K<sub>p</sub>\_prod signal but in integration section accumulation(i.e past error with present error) of the error is multiplied by gain K<sub>i</sub> to produce Ki \_prod and the subtraction of the past error from present error generated result is multiplied by  $K_d$ \_prod. Addition of  $K_i$ \_prod,  $K_d$ \_prod and  $K_p$ \_prod generates vout which is given to the system to control

Coefficient Generation for low Pass Noise Removal Filter:

Low Pass filter.

The filter coefficients are generated by mat lab by given process below

Start  $\rightarrow$  Mat lab  $\rightarrow$  toolboxes  $\rightarrow$  filter design HDL coder  $\rightarrow$  filter design and analysis tool (FDA tool). Open FDA tool then select as shown

🛃 Filter Design & Analysis Tool - [untitled.fda \*] File Edit Analysis Targets View Window Help D 🛎 🖬 🚑 💽 🖉 🖉 X 🛅 🔛 🔽 💀 🐭 🛠 🗇 🗂 🌐 😡 🛈 🖸 🥂 - Magnitude Response (dB) Current Filter Information -Structure: Direct-Form FIR -20 ģ Order: 32 Stable: -30 Yes Source: Designed -40 .60 Store Filter Frequency (kHz) Filter Manager -Response Type Filter Order Frequency Specifications Magnitude Specification: Lowpass Units: Hz Specify order: 32 Enter a weight value for O Highpass 48000 O Minimum order O Bandpass Wpass: 1 O Bandstop Fpass: 9600 Options 1 Vstop: O Differentiator Density Factor: 20 Fstop: 12000 Ŧ Design Method\_ O IR Butterworth • FIR Equiripple F omputing Response ... done

## D.Dayakara Reddy, S.Karunakar Reddy / International Journal of Engineering Research and Applications (IJERA) ISSN: 2248-9622 www.ijera.com Vol. 3, Issue 1, January-February 2013, pp.048-051

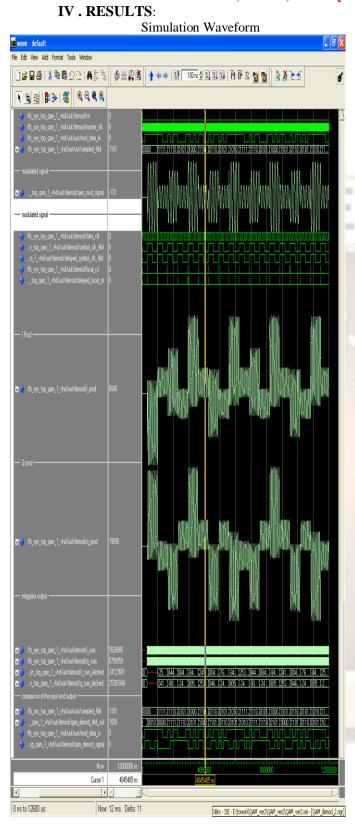

performance of hardware systems but also affectivity and flexibility in design and implementation. Simulation(Modelsim6.2c), synthesis(xilinx ISE), implementation(spartan 3e) and verification of design after implementation is successfully completed.

## REFERENCES

- 16 QAM transmitter and receiver design based on FPGA IEEE 2010, Xuan-thang Vu, Nguyen Anh Duc, Trinh Anh Vu

- [2] C. Dick, F.Harris, M.Rice, Synchronization in Software Radios-Carrier and Timing Recovery Using FPGAs, Proceeding of 2000 IEEE Symposium on Field-Programmable Custom Computing Machines.

- [3] C.Dick, F.Harris, M.Rice, FPGA Implementation of Carrier Synchronization for QAM Receivers, Journal of VLSI Signal Processing, Vol 36, p 57-71,2004.

- [4] Joaquin Garcia, Rene Cumplido, On the design of an FPGA-Based OFDM modulator for IEEE 802.11a, Proceeding of ICEEE, September 7-9, 2005, Mexico.

- [5] John G. Proakis, *Digital Communication*, McGraw-Hill 1993.

- [6] *VLSI for Wireless communication*, Bosco Luen Pearson Education and VLSI series

- [7] http://www.xilinx.com

## V. CONCLUSIONS

A computationally efficient algorithm is developed for a low power and versatile ASIC design of QAM transmission system. Utilization of this algorithm in the development of mobile and portable communications requires not only high