# Fault Detection By Using Random And Deterministic Test Pattern Techniques In A Mixed-Mode BIST Environment

### C.Ravishankar reddy Lecturer, Dr. V. Sumalatha Associate professor, & P.Venkata Gopikumar PG Scholar

Department of Electronics & Communication Engineering Jawaharlal Nehru Technological University Anantapur, India

### Abstract

A method for testing embedded core based system chips is to use a built-in-self-test (BIST). A mixed-mode (Partial pattern matching and multi-control-sequence) built-in-self-test (BIST) that brings two new techniques. They are partial pattern matching and multi control sequence. Partial pattern matching allows the reduction of the number of patterns used for detecting random-pattern-resistant faults without using the fault simulation. A multi control sequence is used to guide the linear feedback shift register (LFSR) to generate these patterns at application time. The main advantages of this method are reduction of the test data volume, require less time to test the application and its reusability for logic cores on a system-on-chip (SOC).

Index Terms—Built in self-test (BIST), Linear feedback shift register (LFSR), random-patternresistant (RPR) faults, system-on-chips (SOCs).

### 1. Introduction

Design integration can be increased by making the ICs small size and power should be low. The requirements for small size and low-power ICs have caused a significant increase in design integration. the integration several designs (cores) into a single monolithic IC which results in a systemon-chip (SOC). The number of cores integrated in a SOC is rapidly increasing, resulting in large amount of test data. To achieve the good test quality for the complex SOC by using the finite number of I/Os is a very difficult task. The amount of time required for this type of test application is high, it is also a big problem to overcome all these drawbacks and for testing embedded core based system chips is to use a built-in self-test (BIST). The advantages of built-in cell-test (BIST) are simplicity, flexibility and low overhead. The test pattern generator for the BIST is pseudorandom (PR) test pattern generator for its onchip test pattern generation.

Pseudorandom test pattern generation (PRPG) can be implemented by using a linear feedback shift register. LFSR has several advantages. They are low overhead, scalability and reuse capability. Faults that are difficult to detect by pseudorandom pattern generation (PRPG) are called random-pattern-resistant (RPR) faults. To increase the probability of detecting the RPR faults by following the three categories. But these three categories have drawbacks

- The modification of circuit under test

- The use of weighted random pattern generation.

- The mixed mode approach.

The first category improves fault coverage by redesigning or inserting test points. It is not always possible because of performance restriction or intellectual property (IP) reasons. The second category is also to increase the probability for test patterns to detect RPR faults, but it is not efficient the third category consists of two phases: In the first phase, PR patterns are applied to detect the faults here fault coverage is done by 60% to 80% only. In the second phase, deterministic test patterns are injected to find the remaining faults. The deterministic patterns are generated by the LFSR[1] by reseeding are Appling a control signal that matches the output of the LFSR to the desired deterministic patterns.

A new technique for the generation of the test patterns for RPR faults by controlling the LFSR at the time of test application. This technique is called partial pattern matching. Select a BIST[2] using a controllable LFSR with multiple scan chains to generate deterministic patterns. In this approach, the system integrator is able to develop the core's tests without knowing the actual implementation of the core because providing deterministic test patterns and the S-matrix by the core provider. Hence, the method promotes design and test reuse without changing or revealing IP information.

Partial-matching technique along with multiple scan chains the BIST greater using a controllable LFSR, the goals such are

- $\succ$  To reduce the test data volume

- $\succ$  To shorten the test application time

- Reusability for logic cores

These three major goals can be achieved by mixed mode BIST. When comparing this method mixed-mode BIST environment to other mixed-mode approaches. In

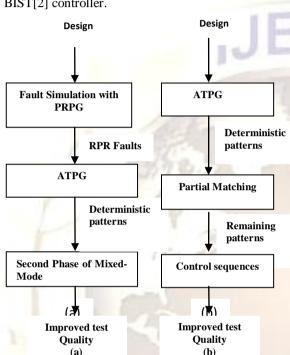

Most mixed modes, the test flow is outlined in Fig. 1(a).

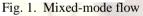

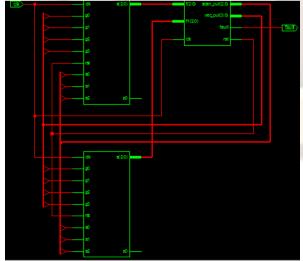

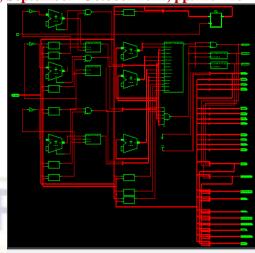

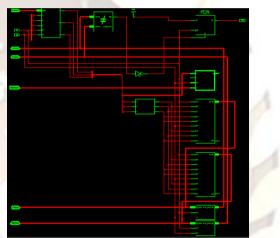

Our methodology is shown in Fig. 1(b): First, a deterministic ATPG is used. The patterns are then partially matched. The remaining patterns are generated by applying a control sequence to the LFSR[1]. In our architecture shown in Fig. 2: It consists of controllable LFSR and phase shifter and scan chains and it is connected to the multi input signature register(MISR) from this it is connected to embedded memory from this it is connected to BIST[2] controller.

In many of the mixed modes, first the test flow is done by using a PR pattern, fault simulation is performed, and the RPR faults are identified. Then, a deterministic automatic test pattern generation (ATPG) is used to generate patterns for RPR faults.

Fig. 2. Proposed testing architecture.

The second phase of the mixed-mode approach is then applied that is deterministic patterns are applied to target remaining faults. In our methodology first, a deterministic ATPG is used. The patterns are then partially matched. The remaining patterns are generated by applying control sequence to the LFSR. In our proposed method there are many advantages. First, fault simulation is eliminated but it is not in the case of other mixed modes. Second, the

partial pattern matching increases the number of hits and hence leaves a fewer number of RPR patterns to require LFSR control signals. The shorter the control sequence, the smaller the storage needed on the chip. In section II, we describe the partial matching scheme. In section III, we describe the multiplecontrol sequence(MCS). Simulation results are presented in section IV, synthesis results are presented in section V, and in section VI, we present our results.

### 2. PARTIAL MATCHING

To maximize the fault coverage, all specified bits of the deterministic test patterns have to be fully matched by the PR patterns being produced by the LFSR. If there are many specified bits in the test pattern of a long scan chain, but it is difficult for PR pattern to hit any deterministic patterns with a full pattern match. This will result in huge number of test patterns that are not covered, this drawback can be eliminated in our new partial matching technique which analyzes the binary Smatrix. This binary S-matrix and utilizes the topology of the logic cones. This approach increases the possibility of patterns matching and hence reduces the size of the required control sequence. *Circuit Modeling*

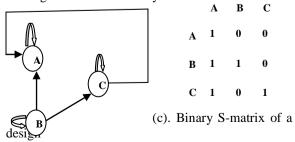

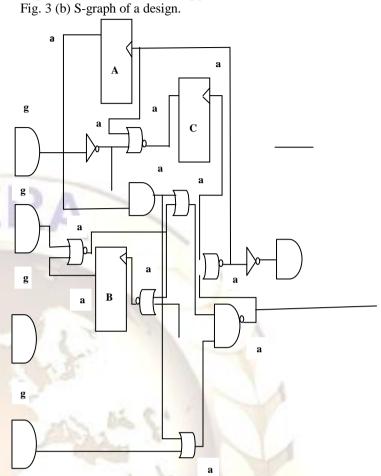

The binary S-matrix can be constructed from the S-graph [6] that is G = (V, E), where V is the set of vertices representing the scan cells in the circuit, E is the set of edges representing connectivity between the scan cells. The first step of the test preparation is to generate the binary S-matrix [6] for the cores. An entry S (i, j) =1 indicates that scan cell i is feeding into scan cell j. And S (I, j) =0 indicates that scan cell i is not feeding into scan

cell j. Using the S-matrix confirms our approach with respect to testing without revealing IP information because the S-matrix is represented by the connectivity of scan cells without giving structure of the logic circuits.

In the similar way the scan chains can also be constricted, in such way that the scan cells in the same scan chain are independent of each other. The aim was to make the set of linear equations, which are necessary for the reseeding of an LFSR. In other words all the inputs of any logic cone are always in one scan chain but in our approach where the inputs of a logic cone can be in any scan chain

Fig. 3. (a) ISCAS benchmark circuit S27.

### **Using Logic Cones to Partition**

A single deterministic test pattern generated by an ATPG usually detects more than one fault in the desire. When the pattern is captured by the flipflops, the new input of any flip flop represents the response of pattern for faults within the combinational circuit cone converging at this flip flop. Logic cones are nothing but logic gates or simply combinational circuits each sub pattern corresponds to a logic cone of the design, which may contain multiple faults of the logic gates. For example deterministic test pattern expanded into three sub patterns each sub pattern detects faults in the corresponding logic cone sub patterns have more "don't care" bits than the original pattern. Hence, they are easier to match with the PR patterns then the original deterministic test pattern. Now a partial pattern matching technique is to be applied to the sub patterns as an enhancement to the full pattern matching technique, which has been applied to the original deterministic test patterns.

The partial matching technique consists of the following three steps.

- Form sub patterns for each deterministic pattern using a cone-masking approach.

- Generate the PR test patterns by simulating the LFSR and match them to sub patterns.

• Combine the remaining unmatched sub patterns that are related to the each original deterministic test pattern and update the final set of deterministic test patterns.

pattern counter counts the number of capture cycles that occur during each test execution phase.

The original deterministic test patterns are split in to sub patterns for each deterministic test pattern the number of sub patterns is equal to the number of columns of the S-matrix that have at least one entry of a "1". The value of bit i of sub pattern j is the same as the value of bit i of the deterministic test pattern if and only if S [i, j] is 1 otherwise it is unspecified bit(x).

In this method, there existing a phase shifter [4] and multiple scan chains. There are two test execution phases. During the first test phase, the LFSR is freely ran for a user specified number of N cycles to generate PR test patterns for easily detectable faults. The number of PR test patterns is the same as the used in all cores but with less test application time because of multiple scan chains. In the second test phase MCSs are used to direct the LFSR to generate the remaining patterns to detect the RPR faults.

Along with the phase shifter [4] and multiple scan chains there existing also a BIST controller. A pattern counter and a bit counter are part of the BIST controller. The bit counter keeps track of the number of test data bits being shifted into scan chains. The

## TABLE I

Sub patterns for deterministic pattern

| Deterministic<br>Pattern<br>A B C | Sub-Patterns<br>A B C | Logic<br>cone |

|-----------------------------------|-----------------------|---------------|

| 0 1 1                             | 0 x x                 | 1             |

|                                   | x 1 x                 | 2             |

|                                   | x x 1                 | 3             |

The circuit shown in Fig. 3(a) is the ISCAS (International standard circuit and system) benchmark circuit S27. It can be represented by the S-graph shown in Fig. 3(b). The corresponding binary S-matrix is shown in Fig. 3(c). As per our methodology first Deterministic ATPG is used and it is found that as 011. This deterministic pattern is then split into three sub-patterns. Each sub pattern corresponds to a logic cone of the design. Number of logic for the circuit in Fig. 3(a), Table I shown deterministic test pattern (column 1) expanded into three sub-patterns. In the circuit fault was injected at

the a3 this fault is not identified by the random pattern and it is detected by deterministic pattern at the 011.once after finding the deterministic pattern and again the faults are injected at the a3, a4 and these faults are determined by random pattern and those faults which are not covered by random pattern are identified by deterministic pattern test generation. Thus all the faults will be determined by this method, by applying both random pattern test generation and deterministic pattern test generation, when s=0 the controllable LFSR [3] generate random test patterns and when s=1 it will generate the deterministic test patterns.

### **3. MULTICONTROL SEQUENCES**

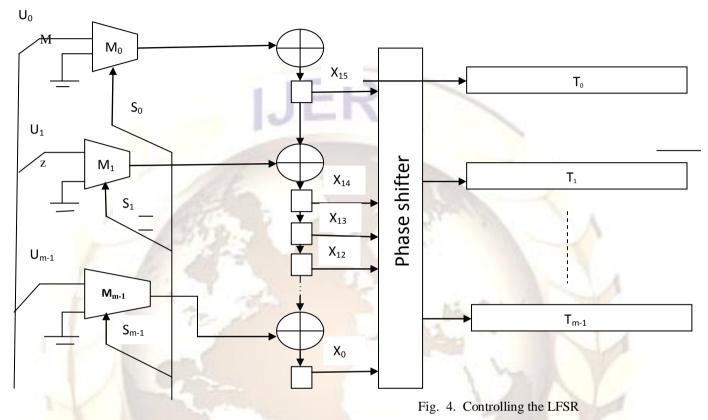

BIST controller allows the LFSR to freely run for a user defined number of capture cycles N it begins to control the LFSR.The method of deterministic bits presented a PRPG register to feed the LFSR seeds for generating the desired patterns in a multiple scan chain design For controlling the LFSR, using an MCS to direct it and to generate and apply the desired deterministic patterns in a multiple scan design. The MCS consists of two vectors U=  $(U_0, U_1, U_2....U_{m-1})$  and S=  $(S_0, S_1, S_2...., S_{m-1})$ . The U vector was directly injected through multiplexers to scan chains. All multiplexers have been moved to the front of LFSR to improve both the test time and test data volume.

Phase shifters structure is based on the STUMPS architecture, one of the scan chains [5] is directly fed from the left most tap of the LFSR while other chains are fed from the phase shifter all the patterns supplied to each scan chains can be controlled. For example assume that four scan chain being controlled by four taps from the phase shifter deterministic test patterns indicated on These scan chains are  $(T_0, T_1,$ T<sub>2</sub>, T<sub>3</sub>) respectively. There are more advantages in using multi control to guide the LFSR to feed the target test data to the scan chains. In most of the cases only a few control sequences in some scan chains have to be specified while the remaining contents in the scan change are automatically matched to deterministic patterns. Therefore the rest of control sequences do not need to be specified. This further reduces the test data storage requirement.

The data format for the MCS consists of two and fields: a header and a body. The header specifies the logic values for the multiplexer selectors, body holds the MCSs  $U_0$ ,  $U_1$ .... $U_{m-1}$ . If the deterministic pattern for the ith scans chain consists of only unspecified bits then the corresponding ith control sequence  $U_i$  is not needed to create the desires values of deterministic patterns. Therefore, Si is equal to zero,  $U_i$  can be skipped from the body field. However even If there is only one specified bit to be controlled in a deterministic pattern the corresponding control sequence  $U_i$  must be include in the body field  $S_i$ , and  $S_i$  is equal to one the advantage of MCS is to control any number of scan chain.

### 4. Simulation results

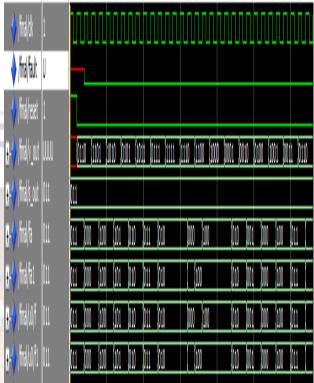

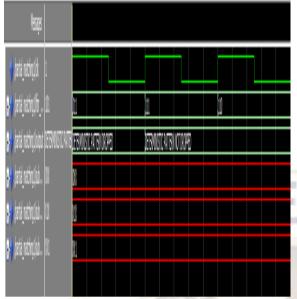

Fig. 5. Random pattern test generation.

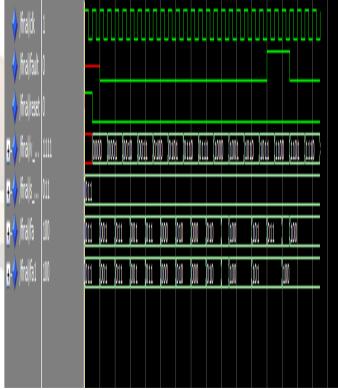

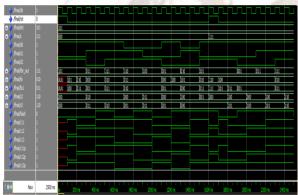

Fig. 6. Deterministic test pattern generation.

Fig. 7. S-graph and S-matrix.

Fig. 8. ISCAS benchmark circuit S27.

5. Synthesis result

Fig. 9. Random pattern test generation

Fig.10.S-matrix and deterministic test pattern generation.

Fig. 11. ISCAS benchmark circuit S27.

### 6. Conclusion

In conclusion, a new approach that is mixed-mode BIST that makes use of a partialmatching technique to facilitate the generation of patterns for RPR faults. The test application mode uses a controllable LFSR for a multiple-scan-chain configuration. We have analyzed the design through the creation of a binary S-matrix and the identification of logic cones. Then, we have applied the partial pattern matching to filter the RPR faults. In addition, we have generated an MCS to guide the LFSR to generate the desired patterns instead of applying the whole deterministic test. the fault coverage as high as intended by the deterministic test, we have succeeded in reducing both the test data volume and the test application time. Moreover, in comparison with [22], both the test sequence length and the hardware overhead are much lower.

### 7. Acknowledgment

P.Venkata GopiKumar would like to thank C .Ravishankar Reddy, who had been guiding through out to complete the work successfully, and

would also like to thank the HOD, ECE Department and other Professors for extending their help & support in giving technical ideas about the paper and motivating to complete the work effectively & successfully

### References

- [1] B. Koenemann, "LFSR-coded test patterns for scan designs," in *Proc. Eur.Test Conf.*, 1991, pp. 237–242.

- [2] E. Kalligeros, X. Kavousianos, and D. Nikolos, "Multiphase BIST:A new reseeding technique for high test-data compression," *IEEETrans. Comput.-Aided Design Integr. Circuits Syst.*, vol. 23, no. 10,pp. 1429–1446, Oct. 2004

- [3] D. Kay and S. Mourad, "Controllable LFSR for built-in self-test," in *Proc.IMTC*, 2000, pp. 223–229

- [4] J. Rajski and J. Tyszer, "Design of phase shifters for BIST applications,"in *Proc. VTS*, 1998, pp. 218–224.

- [5] T. Reungpeerakul, D. Kay, and S. Mourad, "Interactive BIST for embeddedcore in SOC: Partial matching and control sequences technique," in*Proc. IMTC*, 2006, pp. 365–369.

- [6] B. Greene and S. Mourad, "Partial scan testing on the register-transferlevel," in *J. Electron. Test., Theory Appl.*, Dec. 2002, vol. 18, no. 6, pp. 613–626.