Sakshi, et. al. International Journal of Engineering Research and Applications www.ijera.com ISSN: 2248-9622, Vol. 12, Issue 6, (Series-I) June 2022, pp. 28-31

RESEARCH ARTICLE

**OPEN ACCESS**

# **Design Analysis of Full Adder using Cascade Voltage Switch Logic**

Sakshi<sup>1</sup>, Shaveta Bala<sup>2</sup>

<sup>1</sup>(*M tech, ECE Department, Universal Institute of Engineering & Technology, Lalru, India*) <sup>2</sup>(Assistant Professor, Electrical Department, Universal Institute of Engineering & Technology, Lalru, India)

## **ABSTRACT:**

This paper depicts a new design for full adderwith the help of cascade voltage switch logic. Like subtractors we can say adders are also used as basic building block because it is used for all the functional units of microprocessors and digital signal processors. In this modern world of nanotechnology, it is very obvious to designtechniquewhich helps in reduction of area and power consumption. CVSL is a modern technique who meets requirement i.e. high density with minimum delay. The circuit is configurated at 45nm technology and compared with standard cell full adder (45nm technology). Then, circuit comparison on the basis of different parameters is done.

Keywords - Circuit Simulation, CMOSFET Circuits, CVSL, Full Adder.

Date of Submission: 20-05-2022

Date of Acceptance: 03-06-2022

## I. INTRODUCTION

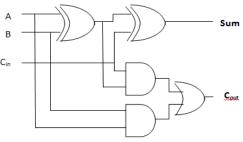

Adders also known as summers are one of the most used logic components used in the design of VLSI circuits. Summationis commonly used arithmetic logic operation. Adders and subtractor are designed by same methodologies. Summer or Adder in digital electronics, a name represents, circuit in which output depends on addition of two inputs [1]. Apart from its basic function i.e. summation, the adderused for many complex circuits like the multiplexers, encoders, to RAMs, address basic calculations and etc. There are mainlytwo types of adders: Fulladder and Halfadder. The half adder is the simple combinational type of adderwhich used to perform basic addition of two input bits. Itgenerates two outputs, sum and carry. The Fulladder is the complex combinational type of summation circuit [2]. It involves three input bits, two normal input bits along with carry as third input. It generates two outputs, sum and carry out. The difference between these two types of adders is that the halfadder uses 2 inputs whereas full adder uses 3 inputs. This paper deals in the study of full adder. The logic gates which are required to form full adder are XOR, AND gates and OR gate [3]. Full adder can also be made up of using nine (9) NAND gates. A full adder can also be constructed using two half adders. The digital circuits who performs subtraction or addition, full adder remains centre to those circuits. In layman terms, full adder plays very vital role in performing any digital circuitry.In the figure shown below, A, B and Cinare input, where A and B are operands to be added, and Cinis the carry bit.Thelogic gate arrangement and truth table for full subtractor is as shown in Figure 1 and Table1 respectively [4].

Figure 1:BasicFull Adder

| Table1: Truth T | able | function | for l | Full | Adder |

|-----------------|------|----------|-------|------|-------|

|-----------------|------|----------|-------|------|-------|

| Α | В | Cin | Sum | Cout |

|---|---|-----|-----|------|

| 0 | 0 | 0   | 0   | 0    |

| 0 | 0 | 1   | 1   | 0    |

| 0 | 1 | 0   | 1   | 1    |

| 0 | 1 | 1   | 0   | 0    |

| 1 | 0 | 0   | 1   | 0    |

| 1 | 0 | 1   | 0   | 1    |

| 1 | 1 | 0   | 0   | 1    |

| 1 | 0 | 1   | 1   | 1    |

Sakshi, et. al. International Journal of Engineering Research and Applications www.ijera.com ISSN: 2248-9622, Vol. 12, Issue 6, (Series-I) June 2022, pp. 28-31

The sum equation is,

$SUM = A \bigoplus B \bigoplus C_{in}$ The carry equation is,

CARRY (  $C_{out}$ )= A.B + ( $C_{in}$  . (A  $\bigoplus$  B))

Full adders are mainly used for Arithmetic logic unit (ALU) in computers to perform addition& GPU for the graphics applications to decrease the circuit complexity [5-6].

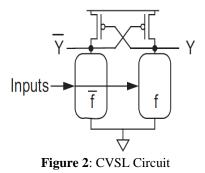

#### II. CASCADE VOLTAGE SWITCH LOGIC

The Cascade Voltage Switch Logic an acronym for CVSL. It is a widely used logic in the design of logic circuits wherein we get 2 outputs for a given input [7]. The cascade voltage switch logic is a type of logic circuit in which two types of input is required true and compliment. In its designing 2complimentary NMOS structures are designed and then attached to a pair of cross-coupled pull-up PMOS transistors [8]. There are to type of CVSL circuit fabricated static and clocked. The cascade voltage switch logic has two nodes instead of one for each gate, which results in high tolerance. The basic gate level CVSL design is shown below in figure 2 [9-10].

Working of above circuit is shown below:

- 1. For any input, one of the networks(pull down) will be ON and the other will remain OFF.

- 2. The network which is ON will generate LOW output. The low output helps to turn ON the PMOS- transistor to generate opposite output high [11].

- 3. The opposite high output, turns the other PMOS transistor OFF so no static power dissipation occurs [12].

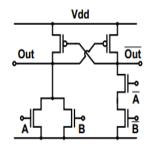

For basic understanding, CVSL implementation with NOR or OR logic is shown below in figure 3 below with a voltage source  $V_{dd}$  applied to it. The logic is generated between two

inputs A & B and the output is generated for OR and NOR logic at terminal A' and B' [13-14].

Figure 3 : OR/NOR implementatuion in CVSL

#### III. CVSL DESIGNS

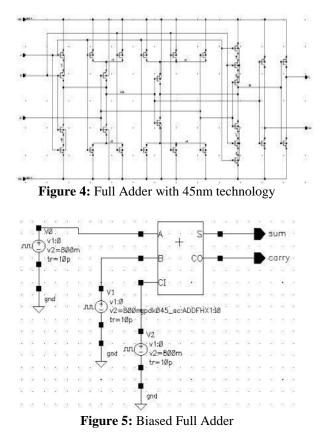

The configuration and inference of the full adder is done using the CVSL (cascade voltage switch logic) in CADENCE software. The schematic is constructed using 45nm technology. The full adderlogic output is obtained. The schematic for the standard gpdk 45 nm CMOS based Full adder is as shown below in figure 4.

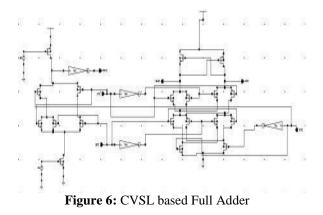

On the basis of CVSL full adder using 45 nm technology is shown below in figure 6.

#### **IV. RESULT SIMULATION**

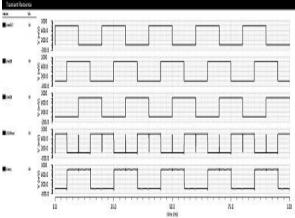

The output waveforms of the normal adder and CVSL based Full adder design are done using same standard i.e. 45nm to maintain symmetry. The waveforms obtained for normal adder is shown below in figure 5.

Figure 5: Full adder Output Waveform in 45nm

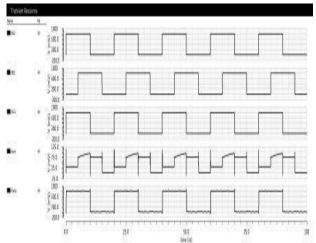

The CVSL based full adder waveform is shown in figure 6.

Figure 6: CVSL based Full adder output waveform

Above described, adderwas designed, and analysis was done and both deigned are compared below depending upon two most important parameters. Parameters are power consumption; number of transistors and propagation delay are counted. The comparison is shown below in the Table 2.

| Table 2: Parameter Comparison for Full Adder. |                        |                        |      |  |

|-----------------------------------------------|------------------------|------------------------|------|--|

|                                               | Power consumption (nW) | Propagation Delay (ns) | Trai |  |

| Circuit                 | Power consumption (nW) | Propagation Delay (ns) | Transistor Count |

|-------------------------|------------------------|------------------------|------------------|

| Conventional Full Adder | 15.63                  | 110.0 ns               | 29               |

| CVSL Full Adder         | 18.942                 | 67.228                 | 27               |

## V. CONCLUSION

From the design and analysis done for the standard and CVSL based design of Full Adder, it has been studied that the CVSL based design provided much less Power consumption whose value for CVSL design is 18.943nW which is much less than 24.146nW, being the power consumption of conventional design. In addition, the delay time during simulation is only 67.22ns, which is also much better than conventional design delay,

which is 110 ns. Thus, the CVSL design is a better choice for the efficient design of Full Adder for use in complex circuit design.

#### REFERENCES

Kumar, Pankaj, Sharma, Rajender Kumar, "An Energy Efficient Logic Approach to Implement CMOS Full Adder", Journal of Circuits, Systems and Computers, Vo. 26, No. 5, pp.1750084-1- 1750084-20, May 2017.

- [2] Marshal Raj, Lakshminarayanan Gopalakrishnan & Seok-Bum Ko, "Design and analysis of Novel QCA Full Adder Subtractor", International Journal of Electronics Letters, pp. 287-300, Febuary 2020.

- [3] Pradeep Kumar, "Existing Full Adders and Their Comparison on The Basis of Simulation Result And to design a improved LPFA (Low Power Full Adder)", International Journal of Engineering Research and Applications, Vol. 2, Issue 6, pp. 599-606, Nov-Dec 2012.

- [4] Vandana Choudhary, Rajesh Mehra, "2- Bit Comparator Using Different Logic Style of Full Adder", International Journal of Soft Computing and Engineering (IJSCE), Vol. 3, Issue 2, pp. 277-279, May 2013.

- [5] Abutaleb, M. M.. "A new static differential design style for hybrid SET–CMOS logic circuits", Journal of Computational Electronics, 2015.

- [6] Abutaleb, M. M.. "A new static differential design style for hybrid SET–CMOS logic circuits", Journal of Computational Electronics, 2015.

- [7] Hiroshi Hatano, "Single Event Effects on Static and Clocked Cascade Voltage Switch Logic (CVSL) Circuits", IEEE Transactions On Nuclear Science, Vol. 56, Issue. 4, pp. 1987-1991, Aug 2009.

- [8] Hiroshi Hatano, "SET Immune Spaceborne CVSL and C2VSL Circuits", Journal of Electrical and Control Engineering, Vol. 3, Issue 5, pp. 43-48, 2013.

- [9] Magdy A. Bayoumi. "Feedback-Switch Logic (FSL): A High-Speed Low-Power Differential Dynamic-Like Static CMOS Circuit Family", 9th International Symposium on Quality Electronic Design, March 2008.

- [10] Priyadarshini.V, "Power-Area trade-off for Different CMOS Design Technologies", Int.J.Computer Technology & Applications, Vol 3, Issue 4, pp. 1388-1394, july-August 2012.

- [11] Dae Woon Kang, Yong Bin Kim, "Design of Enhanced Differential Cascade Voltage Switch Logic (EDCVSL) Circuits for High fan In Gate", IEEE, pp 309-313, 2002.

- [12] D. Somasekhar, K. Roy, "differential Current Switch Logic: A low power DCVS logic family", IEEE J. Solid-State Circuits, Vol. 31, pp. 981-991, July 1996.

- [13] Dae Woon Kang, Yong Bin Kim, "Design of Enhanced Differential Cascade Voltage Switch Logic (EDCVSL) Circuits for High fan In Gate", IEEE, pp 309-313, 2002.

- [14] Huang, PengCheng, Chen, ShuMing, Chen, JianJun, Wu, ZhenYu, Liang, ZhengFa, Hu, ChunMei, Liang, Bin, Liu, BiWei, "Simulation study of N-hit SET variation in differential cascade voltage switch logical circuits", Science China Press and Springer-Verlag Berlin Heidelberg, Vol. 58, Issue 2, pp. 287-300, 022401:1–022401:9, Febuary 2015.

# AUTHORS

Er. Sakshi is currently pursuing MTech. degree from Universal Institute of Engineering & Technology, Lalru, Punjab, India. She has completed her B. Tech from Kurukshetra University, Kurukshetra, India. She is having a total of five years of experience of industry experience. Her areas of interest include Advanced Digital Signal Processing, Wireless Networks and Image Processing.

Shaveta Bala, is currently working as an Assistant Professor in the Department of Electrical Engineering. She is currently working in Universal Institute of Engineering & Technology, Lalru, Punjab, India.