# **RESEARCH ARTICLE**

**OPEN ACCESS**

# Power Analysis of CMOS Combinational Logic Circuits Using Adiabatic Reduction Technique at 180nm Technology

Pooja Chaudhary<sup>1</sup> and Dipti Girdhar<sup>2</sup>

<sup>1,2</sup>Department of Electrical, Electronics & Communication Engineering, ITM University, Gurgaon, (Haryana), India

#### Abstract

In recent years the adiabatic techniques have been used to reduce power consumption in various high end processors. Various adiabatic logic circuits have been proposed based on the energy recovery principle. The term "adiabatic" is derived from a reversible thermodynamic process and it stands for a system where a transformation takes place in such a way that no gain or loss of heat or energy occurs. This paper discusses an energy efficient way of designing the combinational logic circuits using adiabatic technique to minimise the power consumption. A comparative analysis for power consumption between conventional CMOS designs of the AND, NAND, OR, Inverter Logic and their adiabatic designs has been performed at 180nm. A power saving of up to 33% in AND gate, 16% in NAND, 6% in NOR and 5% in Inverter respectively is observed at  $V_{DD}=1.8V$ , and  $T=27^{0}C$ .

Key Words: Adiabatic circuits, AND Logic, Combinational Circuits, Inverter, Low-Power, NAND Logic, OR Logic.

[5]

## I. INTRODUCTION

In today's world Power reduction is one of the major concern in designing in VLSI using various methodologies because of two major reasons one is the long battery life requirement in digital equipment and in mobiles also and second is high power dissipation due to increase in number of transistors on a chip which results in problems in IC packaging and reliability [1].

Adiabatic logic uses AC power supply instead of constant DC supply and this is one of the main reasons in the reduction of power dissipation. The main idea in an adiabatic charging is that transitions are considered to be sufficiently slow so that all the nodes are charged or discharged at a constant current. In this way power dissipation is minimized by decreasing the peak current flow through the transistors.Use of adiabatic logic circuits with energy recovery scheme has received considerable attention in high performance low-power applications [2,3,4].

In this paper, the section II, discusses the review of previously reported work on power calculation in different combinational circuits. In section III, the designing and simulation of various combinational logic units like NAND, AND, OR and INVERTER has been performed and power consumption analysis is performed using adiabatic reduction techniques. Finally the conclusion has been discussed in section IV.

#### II. A REVIEW OF RELATED WORK

Various adiabatic power reduction techniques, e.g., Complementary Pass Transistor Logic, Two phase clocked adiabatic static CMOS logic, Two phase adiabatic dynamic CMOS logic, Adiabatic dynamic CMOS logic NOR, Quasi-static energy recovery logic NOR gate techniques etc. has been proposed by the researchers. A brief description of some of these techniques is as.

# i. High Performance Sequential Circuits with Adiabatic Complementary Pass-Transistor Logic

The sequential circuits are implemented using Pure NMOS Transistors and the 4-Bit Shift Register is realized with Complementary Pass Transistor Logic and after implementation the Adiabatic D & JK flipflop designs are proposed [5].

The analysis is performed on Cadence design tools. The power saving analysis is shown in Table1.

| Schematic<br>Diagram | Power Saving | Power Saving  |  |

|----------------------|--------------|---------------|--|

| Flip Flop            | CPAL Logic   | 2N-2N2P Logic |  |

| D                    | 81%          | 88%           |  |

| JK                   | 13% to 68%   | 69% to 91%    |  |

### Table 1: Power saving of different Sequential Circuits

# ii. Analysis of Adiabatic Logic NOR Gate for Power Reduction

A NOR gate design is discussed using adiabatic reduction technique using five techniques namely Two phase clocked adiabatic static CMOS logic, Two phase adiabatic dynamic CMOS logic, Adiabatic dynamic CMOS logic NOR, Quasi-static energy recovery logic NOR gate techniques is studied [6]. According to the analysis done the 2PASCL NOR logic gives lowest dissipation power at frequency 10 to 1000MHZ. The simulations are performed using Tanner Tool Version 13 on  $0.18\mu$ m. A constant output load capacitance of 1pf is used for power and delay measurement. CMOS technology and transient analysis is done at 1.8v supply voltage which is shown in Table2.

| Γ | Input | Input | 2PASCL   | 2PADCL   | ADCL   | QUASSI   |

|---|-------|-------|----------|----------|--------|----------|

|   | А     | В     |          |          |        |          |

| Γ | 0     | 0     | Weak 0   | Weak 1   | Strong | Strong 1 |

|   |       |       |          |          | 1      |          |

|   | 0     | 1     | Strong 0 | Strong 0 | Strong | Strong 0 |

|   |       |       |          |          | 0      |          |

|   | 1     | 0     | Strong 0 | Strong 0 | Strong | Strong 0 |

|   |       |       |          |          | 0      |          |

|   | 1     | 1     | Strong 0 | Strong 0 | Strong | Strong 0 |

|   |       |       |          |          | 0      |          |

Table 2: Transient Simulation Results [6]

### III. SIMULATION OF ADIABATIC LOGIC CIRCUITS: AND, OR, NAND, & INVERTER

In this section the study and implementation of combinational logic units using adiabatic logic and conventional CMOS techniques at transistor level is carried out along with the Power analysis. The following parameters are taken in to account while designing.

Table 3: Width (W) and Length (L) for NMOS and PMOS

| Technology | 180nm |

|------------|-------|

| W(NMOS)    | 2µm   |

| L(NMOS)    | 18µm  |

| W(PMOS)    | 2 µm  |

| L(PMOS)    | 18 µm |

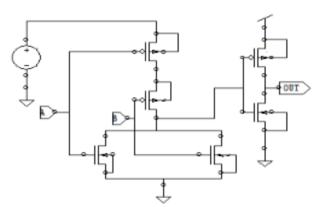

Figure 1: Schematic of Adiabatic NAND Gate

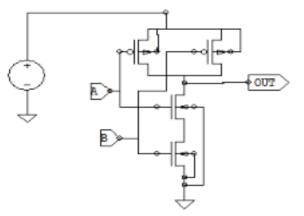

Figure 2: Schematic of Adiabatic OR Gate

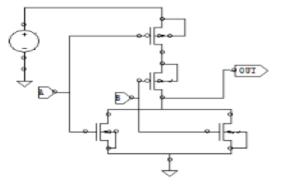

Figure 3: Schematic of Adiabatic AND Gate

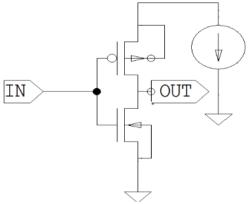

Figure 4: Schematic of Adiabatic Inverter Circuit

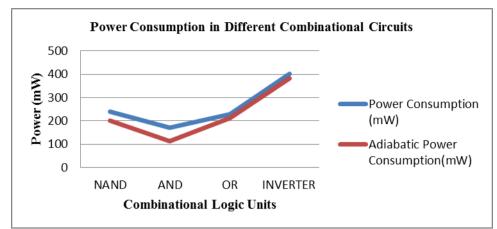

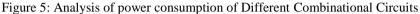

The power consumed for conventional CMOS circuits and with Adiabatic power reduction technique for NAND, AND, OR gate and Inverter is calculated on 180nm technology with 1.8 Volt supply. The graphical representation of power consumption in different Combinational Circuits is shown in Figure 5 along with the percentage of power reduction of the combinational logic units Figure 6.

Figure 6: Analysis of % of power consumption of Different Combinational Logic units

### **IV. CONCLUSIONS**

In this analysis, it is investigated that the AND gate has the highest level of power reduction of 33.4% whereas Inverter with lowest level of power reduction of 4.72% at adiabatic logic level. A power reduction of 15.6% and 6.1% is seen at NAND and OR logic units. All the parameters are computed on Cadence Virtuoso Tool at 180 nm Technology at 1.8V supply voltage. This reduction technique can be used in applications such as Memory Designing, in high performance low power circuits and various high end processors.

#### REFERENCES

- Y. Sunil Gavaskar Reddy and V. V. G. S. Rajendra Prasad "Power comparision of CMOS and adiabatic full adder circuits". URL : <u>http://arxiv.org/ftp/arxiv/papers/1110/1110.15</u> <u>49.pdf</u>.

- [2] D. A. Hodges, H. G. Jackson, and R. A. Saleh, Analysis and Design of Digital Integrated Circuits, McGraw-Hill, New York, NY, USA, 3rd edition, 2003.

- [3] W. C. Athas, L. Svensson, J. G. Koller, N. Tzartzanis, and E. Y. C. Chou, "Low-power digital systems based on adiabatic-switching principles," IEEE Transactions on Very Large Scale Integration (VLSI) Systems, vol. 2, no. 4, pp. 398–407, 1994.

- [4] Y. Moon and D. K. Jeong, "An efficient charge recovery logic circuit," IEEE Journal of Solid-State Circuits, vol. 31, no. 4, pp. 514–522, 1996.

- [5] Ch. Praveen Kumar, S. K. Tripathy and Rajeev Tripathi, "High Performance Sequential Circuits with Adiabatic Complementary Pass-Transistor Logic (ACPL)" IEEE Tencon pp. 1-4, 23-26 Jan. 2009.

- [6] Ritu Sharma, Pooja Nagpaland, and Nidhi Sharma, "Analysis of Adiabatic Logic NOR Gate For Power Reduction" International journal of latest research in Science and Technology, vol.1, Issue 2, page No. 179,182,July-August(2012).

- [7] N. H. E. Weste and D. Harris, CMOS VLSI Design: A Circuits and Systems Perspective,

Addison-Wesley, Reading, Mass, USA, 3rd edition, 2004.

- [8] S. Wisetphanichkij and K. Dejhan, "The combinational and sequential adiabatic circuit design and its applications," Circuits, Systems, and Signal Processing, vol. 28, no. 4, pp. 523–534, 2009.

- [9] A. G. Dickinson and J. S. Denker, "Adiabatic dynamic logic," IEEE Journal of Solid-State Circuits, vol. 30, no. 3, pp. 311–315, 1995.

- [10] C. S. A. Gong, M. T. Shiue, C. T. Hong, and K. W. Yao, "Analysis and design of an efficient irreversible energy recovery logic in 0.18 μm CMOS," IEEE Transactions on Circuits and Systems I, vol. 55, no. 9, pp. 2595–2607, 2008.

- [11] H.H. Wong, K.T. Lau, "Energy-recovery low-power C-PAL flip-flop design" International Journal of Microelectronics, vol 18, no.2, pp. 6-11, 2001.

#### About the Authors

<sup>1</sup>**Pooja Chaudhary,** completed her B.Tech in Electronics and Communication Engineering from Amity University, Noida in 2012. She is now pursuing her Master of Technology (M.Tech.) in VLSI Design at ITM University, Gurgaon (Haryana) India. Her interest includes Digital Design, VLSI Testing and Verification.

<sup>2</sup>**Dipti Girdhar,** an Asst. Professor in Department of Electrical, Electronics and Communication Engineering, ITM University, Gurgaon, (Haryana), India has received her M.Tech. (VLSI Design) from N.I.T,Kurukshetra and B.Tech. (Electronics & Communication Engineering) Degree from the Kurukshetra University, Kurukshetra (Haryana), India in the year of 2010 and 2007, respectively. Her main research interests are in ASIC Design/Verification, Verilog HDL, HVL, and RTL Design. She has four-years of experience in academics and industry.