# A Novel Approach to Design a High Performance Domino Cmos Logic

Lalit Mishra<sup>1</sup>, Nitin Meena Assistant Professor<sup>2</sup>

<sup>1</sup>Department of VISI and Embedded System

<sup>2</sup>Department of VLSI and Embedded System IES College of Technology, RGTU ,Bhopal

#### Abstract

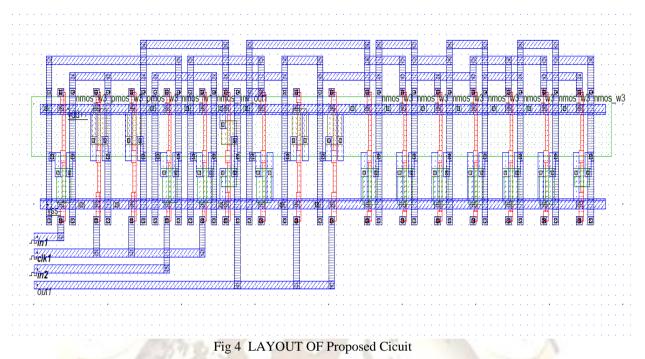

In this paper a Domino Cmos logic circuit is design with aim to reduction in power consumption, time delay and energy efficient. Due to rapid growth in VLSI Technology, an integrated circuit has demand with low power, high performance, compatible, small in size and easy to recodify. Dynamic cmos gates are inherently less resistance to noise than static cmosgate. Sothis approach allow low power, noise tolerant and high performance. Domino cmos logic is a form of dynamic logic that gives output in cascaded form and it consume higher dynamic switching speed, leakage power and noise immunity.This design has weaker Simulated and analyzed on 0.12 Microwind2 tool technology.

**Keyword** – Domino Logic, Dynamic circuit, Delay, Low Power, Noise Tolerant,

#### I. Introduction

Due to continuously increasing chips complexity and number of transistors, circuit's power consumption is growing. Technology trends shows that circuit delay is scaling down by 30%, performance and transistor density are doubled approximately every two years, and the transistor's threshold voltage is reduced by almost 15% every generation. These entire technology trend leads to higher and higher power in circuits .Domino logic is a CMOS-based evolution of the dynamic logic techniques which were based on either PMOS or NMOS transistors. It allows a rail-to-rail logic swing. It was developed to speed up circuits.Domino CMOS logic circuit family finds a wide variety of applications in microprocessors, digital signal processors, and dynamic memory due to their high speed and low device count. However, for wide fan in domino logic, that is when there is a long chain of NMOS transistors.(6)

# II. Review of Domino logic circuit

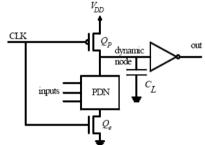

The basic dynamic domino logic gate is shown in Fig 1. As shown in the figure, it consists of a pull-down network (PDN) that realizes the desired logic function and there are two switches in series that are periodically operated by the clock signal, *CLK. CL* denotes the total parasitic capacitance between the dynamic node and ground. When *CLK* is low, *QP* is turned on, and the circuit is in the precharge phase where the dynamic node charges to *VDD*.

Also, during precharge, the inputs are allowed to change and settle to their proper values. Because Qe is off, no path to ground exists. When CLK is high, QP is off and Qe turns on, and the circuit is in the evaluation phase.

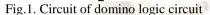

During the evaluation phase; there are two possibilities for the dynamic-node voltage. If the input combination is one that corresponds to a low output, the dynamic-node voltage must be maintained at the supply voltage, VDD. On the other hand, if the input combination is one that corresponds to a high output, the dynamic-node capacitor, CL must be discharged to ground through the conducting NMOS transistors of the PDN. The inverter at the output node is put for allowing this stage to be cascaded with another one. Specifically, if the dynamic node of this stage is connected directly to the gate of an NMOS transistor in the PDN of the next stage and is at logic "1", then this transistor will conduct during the time interval from the time of application of this "1" to the time at which the dynamic-node capacitor, CL discharges below the threshold voltage of this transistor. This causes the dynamic-node capacitor of the second stage to discharge as it mustn't be. The conventional problem that arises during the evaluation phase is that the leakage current through the PDN of CL. Also, the charge of CL may be shared with any of the internal capacitors associated with the NMOS transistors of the PDN. So, a PMOS keeper must be used to replenish the lost charge as show in Fig.2. This keeper must be week so that its current during the evaluation phase is relatively small so that the discharging of CL will not be slowed down.

Lalit Mishra, Nitin Meena / International Journal of Engineering Research and Applications (IJERA) ISSN: 2248-9622 www.ijera.com Vol. 3, Issue 4, Jul-Aug 2013, pp. 462-465

Fig.2. Use of PMOS keeper in domino CMOS

This problem will be more tactile for the case when there is a large number of serially connected NMOS transistors in the PDN. In this case, discharging of *CL* will be very slow due to the keeper contention current.

#### III. Proposed Domino CMOS circuit

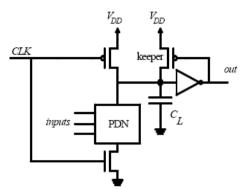

Our proposed technique to speed up the discharging process of the dynamic-node capacitor. The technique uses current mirror of suitable mirroring ratio to achieve the motive and it results in remarkable advances in reducing the time delay as compared to other well known designs

The proposed circuit is designed for two input AND gate with long chain of NMOS transistors and current mirror draws the keeper contention current and speeds up the discharging process.

# IV. Working of proposed circuit

The proposed circuit works in following manner that during the precharge phase, Qewill be deactivated, thus the current through the transistor, M1 will be zero. By the effect of the current mirror formed from M1 and M2, the current of M2 will also be zero allowing CL to charge to VDD. During the evaluation phase, the CLK signal will be at logic "1", thus closing the path to ground. If the inputs status is such that there is no current path through the PDN, the current through M1 and M2 will remain zero, thus leaving CL charged at VDD.

Fig 3 Proposed circuit having current mirror

Likewise, if the inputs status is such that there is a current path through the PDN, the relatively small current through M1 will be mirrored through M2, thus speeding up the discharging process of CL. Increasing the current-mirroring ratio will speed up the discharging process further. The speed improvement gained from this method increases when the number of the series-connected NMOS transistors increases. In case of noise margin, the dynamic-node voltage, VCL will be discharged not to 0 V; instead, it discharges to the threshold voltage of the transistor, M1. So, the threshold voltage of this transistor will be put equal to 0 V. Even if there is an external noise on the gate of this transistor, it will not conduct as the other NMOS transistors of the chain are not conducting. So for very long chain of series-connected NMOS transistors in the PDN, the discharging current through M1 will be relatively small and will decrease with increasing the number of NMOS transistors in the chain. In such circuits, to obtain a significant increase in speed, the current mirroring ratio, iM2/iM1 = (W/L)2/(W/L)1 needs to be increased to a large value, typically 20. Achieving this relatively large current-mirroring ratio by the conventional current mirror will result in an increased capacitance at the gate terminal of M1 and M2, thus slowing down the operation. Also, increasing the current-mirroring ratio to such a large value using the rudimental method causes the

dynamic-node capacitance, CL to increase, thus

degrading the speed further.

# Lalit Mishra, Nitin Meena / International Journal of Engineering Research and Applications (IJERA) ISSN: 2248-9622 www.ijera.com Vol. 3, Issue 4, Jul-Aug 2013, pp. 462-465

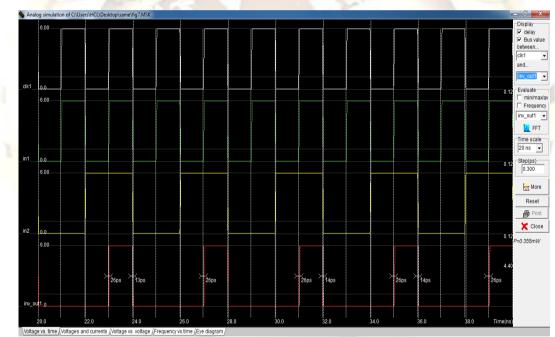

Fig 5 Voltagevs Time Analysis

# V. Conclusion

It will be found that the current mirroring ratio, m of the current mirror must lie within a certain range so that the discharging process will not be adversely affected by the addition of the current mirror. Domino circuits have offered an improved performance in speed and power when compared with CMOS circuit. This range will be determined quantitatively. The simulation results for comparing the conventional and proposed techniques for the 0.12 µm technology are presented. There are an increasing number of applications that require the

use of a large number of NMOS transistors in series in the pull-down network of the CMOS domino logic.

# Reference

- Pretorius J.A., Shubat A.S., Salama C.A.T.Latched domino CMOS logic, Solid-State Circuits, IEEE Journal, Date: Aug 1986, Volume: 21, Issue 4, Page(s): 514 – 522

- [2] Sharma V., Al-Assadi W.K.Analysis and Modeling of Crosstalk Noise in Domino

#### Lalit Mishra, Nitin Meena / International Journal of Engineering Research and Applications (IJERA) ISSN: 2248-9622 www.ijera.com Vol. 3, Issue 4, Jul-Aug 2013, pp. 462-465

CMOS Circuits, Region 5 Technical Conference, 2007 IEEE, Date: 20-22 April 2007, Page(s): 374

- [3] Wurtz L.Scaling procedure for Domino CMOS logic, Southeastcon'92, Proceedings, IEEE. Date: 12-15 Apr 1992, Page(s): 580

- [4] Berg Y.A Novel ultra low-voltage and high speed domino CMOS logic.VLSI System on Chip Conference (VLSI-SoC), 2010 18th IEEE/IFIP. Date: 27-29 Sept. 2010. Page(s): 225

- [5] Sharroush S.M., Abdalla, Y.S., Dessouki A.A., El-Badawy E.S.A.Compensating for the keeper current of CMOS domino logic using a well designed NMOS transistor.Radio Science Conference, 2009 NRSC 2009. Date: 17-19 March 2009. Page(s): 1

- [6] M Hosseinghadiry, H Mohammadi ,MNadisenejani "Two New Low Power High Performance Full ADDER with Minimum gates" Volume 28 -157,2009

- [7] Rjoub A., Koufopavlou O., Nikolaidis S.Low-power/low-swing domino CMOS logic.Circuits and Systems, ISCAS '98.

Proceedings of the 1998 IEEE International Symposium on Date: 31 May-3 Jun 1998, Volume: 2, Page(s): 13

- [8] Zamudio A., Champac V.H., Sarmiento-Reyes A.Design of domino CMOS cells under delay constraint.Mixed-Mode Integrated Circuits and Applications, 1999.Third International Workshop. Date: 1999 Page(s): 106

- [9] De Micheli G. Performance-Oriented Synthesis of Large-Scale Domino CMOS Circuits, Computer-Aided Design of Integrated Circuits and Systems, IEEE Transactions. Date: September 1987, Volume: 6, Issue: 5 Page(s): 751

- [10] Oklobdzija V.G., Montoye R.K. Designperformance trade-offs in CMOS-domino logic.Solid-State Circuits, IEEE Journal.Date : Apr 1986 Volume : 21, Issue:2 Page(s): 304

- [11] Shang-JyhShieh ,Jinn-Shyan Wang Design of low-power domino circuits using multiple supply voltages, Electronics, Circuits and Systems, 2001. ICECS 2001, 8th IEEE International Conference. Date: 2001 Volume: 2. Page(s): 711

- [12] Moradi F., Wisland D.T., Mahmoodi H., TuanVu Cao High speed and leakagetolerant domino circuits for high fan-in applications in 70nm CMOS technology.Devices, Circuits and Systems, 2008.ICCDCS 2008.7th International

Caribbean Conference. Date: 28-30 April 2008 Page(s): 1

- [13] [13] Yeganeh H., DarvishanA.h., Amirabadi A.Noise tunable clock delayed domino logic using latched keeper, Microelectronics, 2007. ICM 2007. Date: 29-31 Dec. 2007 Page(s): 187

- [14] [14] Rave A., Carley L.R., Mixed-swing methodology for domino logic circuits, Custom Integrated Circuits, 2001, IEEE Conference Date: 2001 Page(s): 85

- [15] [15] R.Zimmermann, W.Fichtner Lowpower logic styles: CMOS versus passtransistor logic, IEEE Journal of Solid-State Circuits 32 (7) (1997) 1079–1089.

- [16] [16] Yuan J.R., Svensson C., Larsson P. New domino logic precharged by clock and data, Electronics Letters ,Date : 9 Dec. 1993 Volume : 29, Issue:25

- [17] [17] Kundu R., Blanton R.D.Timed test generation for crosstalk switch failures in domino CMOS, VLSI Test Symposium, 2002. Proceedings 20th IEEE. Date: 2002 Page(s): 379

- [18] [18] Elgharbawy W., Golconda P., Kumar A., Bayoumi M., On gate leakage reduction in dynamic CMOS circuitsCircuits and Systems, 2005. 48th Midwest Symposium Date: 7-10 Aug. 2005 Page(s): 1390

- [19] [19] Natarajan S., Gupta S.K., Breuer M.A., Switch-level delay test of domino logic circuits, Test Conference, 2001. Proceedings. International Date : 2001 Page(s): 367

- [20] [20] Chatterjee B., Sachdev M., Krishnamurthy R., Leakage control techniques for designing robust, low power wide OR domino logic for sub-130nm CMOS technologies Quality Electronic Design, 2004. Proceedings. 5th International Symposium Date: 2004 Page(s): 415